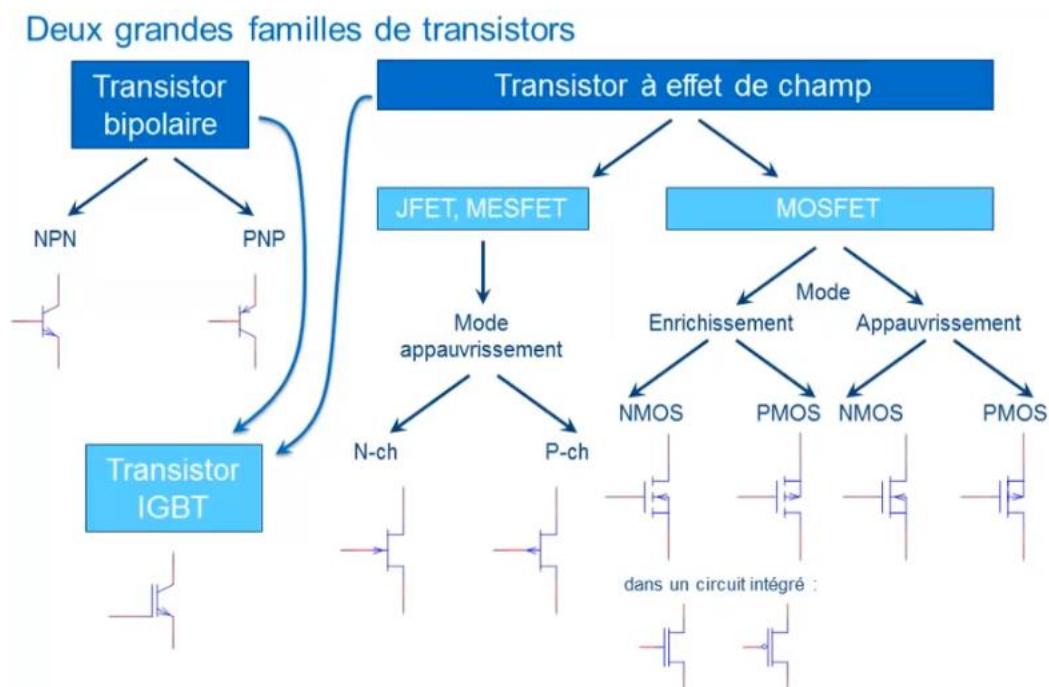

## **CHAPITRE 3 : LES TRANSISTORS**

Les transistors sont des composants électroniques fondamentaux qui jouent un rôle crucial dans l'amplification et le contrôle des signaux électriques dans nos circuits électroniques.

Sans transistors, il serait difficile de construire les appareils et systèmes électroniques complexes qui font désormais partie intégrante de notre vie quotidienne.

Les transistors agissent comme des interrupteurs électroniques et comme des amplificateurs de signal qui nous permettent de tout créer (du simple interrupteur On-Off aux ordinateurs et systèmes puissants). Les processeurs informatiques que nous utilisons contiennent des millions de transistors

## 1. LES TRANSISTORS BIPOLAIRES (BJTs)

Historiquement il est le premier composant actif à semiconducteur, son influence dans l'industrie électronique a été considérable. Le transistor bipolaire peut être considéré du point de vue électronique comme une source de courant commandée par une tension. Ce courant peut alors créer une différence de potentiel aux bornes d'une charge (une résistance par exemple) plus importante que la tension de commande. On dit alors que le dispositif a un gain en tension. Il est facile de comprendre alors qu'il est possible de l'utiliser pour réaliser des amplificateurs électroniques. Quand la variation de tension appliquée en entrée permet de faire passer le

transistor de l'état non conducteur à l'état conducteur, on peut l'utiliser pour réaliser des fonctions binaires. Il a donc été aussi un composant de base de l'électronique numérique. Les transistors bipolaires ont cependant été de moins en moins utilisés à partir des années 80 pour être remplacés par les transistors de type MOSFET offrant des avantages en terme de consommation électrique. Les transistors bipolaires sont encore utilisés pour des fonctions exigeantes en terme de rapport signal sur bruit ou dans des applications d'électronique de puissance.

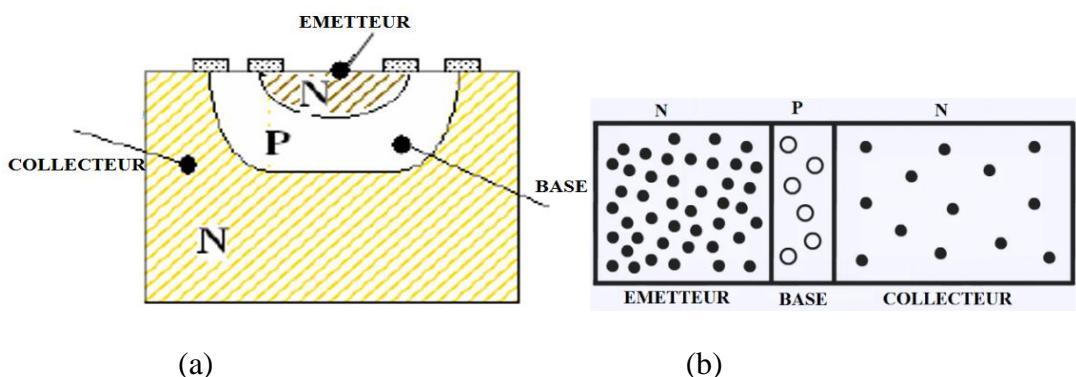

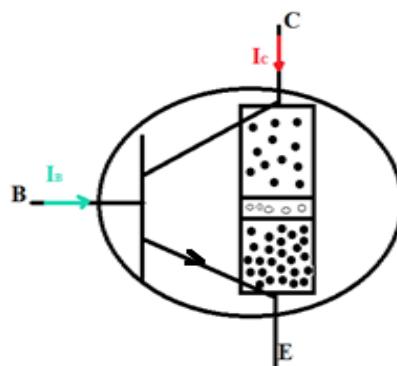

Un transistor à jonction bipolaire est un composant à semi-conducteur constitué de 2 jonctions P-N présentant une région commune. Il est formé de trois zones différemment dopées PNP ou NPN d'un même monocristal semi-conducteur mais pas forcément le même type de dopant, ni le même niveau de concentration. Chacune de ces régions est reliée à une électrode

- L'émetteur est en surface. Il est en général fortement dopé.

- La base est très mince et moyennement dopée

- Le collecteur est situé en-dessous de la base et il constitue deux zones faiblement dopée et très dopée.

Fig 45: (a) Coupe d'un transistor NPN au niveau des jonctions. (b) Son schéma simplifier

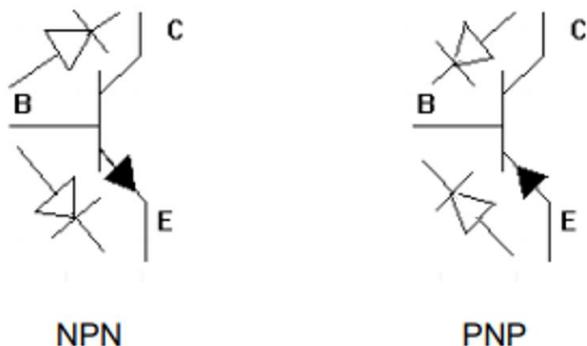

Fig 46: Symboles de transistor NPN et PNP

## 1.1. L'EFFET TRANSISTOR

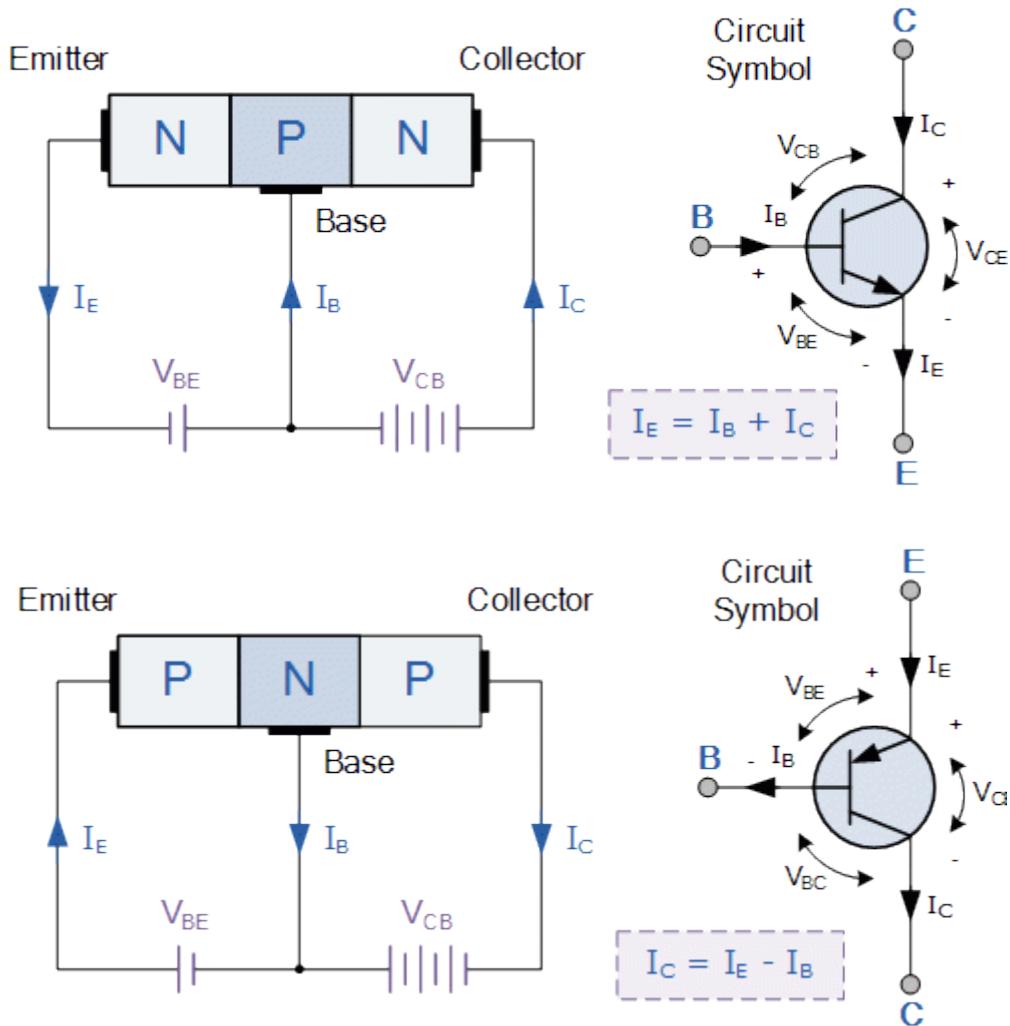

Les transistors bipolaires fonctionnent en utilisant un petit courant de base pour contrôler un grand courant entre l'émetteur et le collecteur. Dans les transistors bipolaires :

Type NPN : le transistor est commandé par un courant positif polarisé à la base pour contrôler le flux de courant du collecteur à l'émetteur

Type PNP : le transistor est commandé par un courant négatif polarisé à la base pour contrôler le flux de courant de l'émetteur au collecteur

Fig 47: Polarisation des transistors NPN et PNP

Dans notre étude on va prendre l'exemple du transistor NPN car il a meilleures performances que les PNP et il est le plus utilisé et le plus facile à réaliser. On peut déduire le principe de fonctionnement du transistor PNP en échangeant les rôles des électrons par des trous et en inversant les signes des tensions d'alimentation et des courants

Dans un transistor bipolaire type NPN, si on applique une tension positive à la borne de la base et une tension négative à la borne de l'émetteur, la jonction base-émetteur sera polarisée en direct et si on connecte une autre batterie entre l'émetteur et le collecteur de telle sorte que la borne d'émetteur du transistor sera connectée à la borne négative de la batterie. La jonction base-collecteur devient polarisée en inverse.

La tension  $V_{CE}$  appliquée entre l'émetteur et le collecteur chute à deux endroits. L'un est au potentiel de la barrière directe à travers la jonction émetteur-base  $V_{EB}$  qui est d'environ 0,7 volt dans le cas de transistors en silicium. La partie restante de la tension appliquée  $V_{CB}$  chute comme une tension inverse à travers la jonction base-collecteur.  $V_{CE} = V_{EB} + V_{CB}$

Dans ces conditions, les électrons libres dans l'émetteur vont traverser la jonction émetteur-base et vont entrer dans la base où ils auront très peu de trous à recombiner. Mais en raison du champ électrique traversant la jonction, les électrons libres migrant depuis l'émetteur reçoivent de l'énergie cinétique et parce que la base est très mince, ils n'auront pas suffisamment de temps pour se recombiner et donc traverser la jonction base-collecteur polarisée en inverse qui favorise le flux d'électrons libres de la base vers le collecteur (les minoritaires). De cette façon, les électrons circulent de l'émetteur au collecteur et, par conséquent, le courant du collecteur vers l'émetteur commence à circuler.

Certains des électrons de l'émetteur se recombinent avec les trous présents dans la base ce qui contribue au courant de base qui est beaucoup inférieur au courant collecteur-émetteur.

L'augmentation de la tension appliquée sur la base entraîne une augmentation considérable du flux d'électrons libres de l'émetteur vers la base avec plus d'énergie cinétique. Cela provoque une augmentation du courant du collecteur. De cette façon, on peut contrôler un grand signal de collecteur en contrôlant un petit signal de base.

Si on considère que  $\alpha$  est le pourcentage d'électrons venant de l'émetteur et qui ont atteint le collecteur avec  $0 < \alpha < 1$ . Alors  $(1-\alpha)$  va être le pourcentage d'électrons venant de l'émetteur et qui se sont recombinés avec les trous de la base. Donc, les courants du transistor  $I_E$   $I_C$  et  $I_B$  sont exprimer comme le suivant

$$\left. \begin{array}{l} I_C = \alpha I_E \\ I_B = (1-\alpha) I_E \end{array} \right\} \text{avec, } I_E = I_B + I_C$$

On déduit  $I_C = \beta \times I_B$  avec  $\beta = \frac{\alpha}{1-\alpha}$  c'est le gain en courant du transistor bipolaire qui est beaucoup plus grand que 1

$$\begin{aligned} I_E &= I_B + I_C = \frac{I_C}{\beta} + I_C \\ I_E &= \frac{(1+\beta)}{\beta} I_C \Rightarrow I_C = \frac{\beta}{\beta+1} I_E \\ \Rightarrow \alpha &= \frac{\beta}{\beta+1} \end{aligned}$$

$\frac{\beta}{\beta+1}$  est légèrement inférieur à 1 donc  $I_E$  est légèrement inférieur à  $I_C$

## 1.2. CARACTÉRISTIQUES ÉLECTRIQUES.

### 1.2.1 Montages de base.

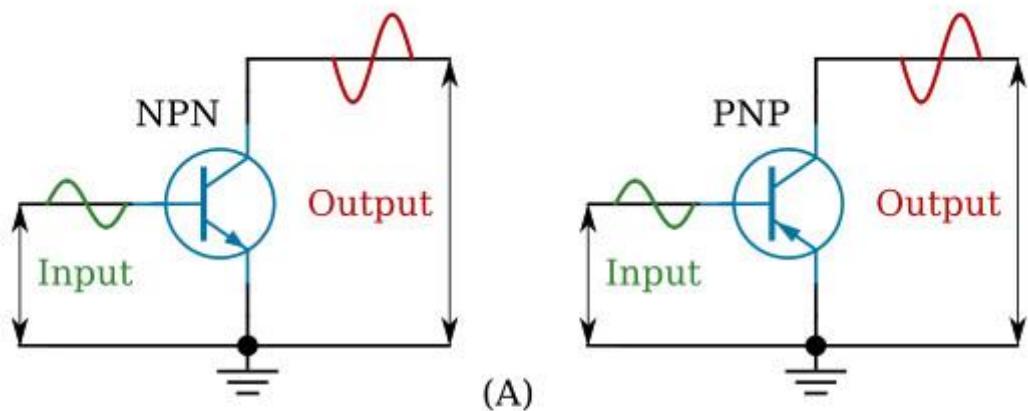

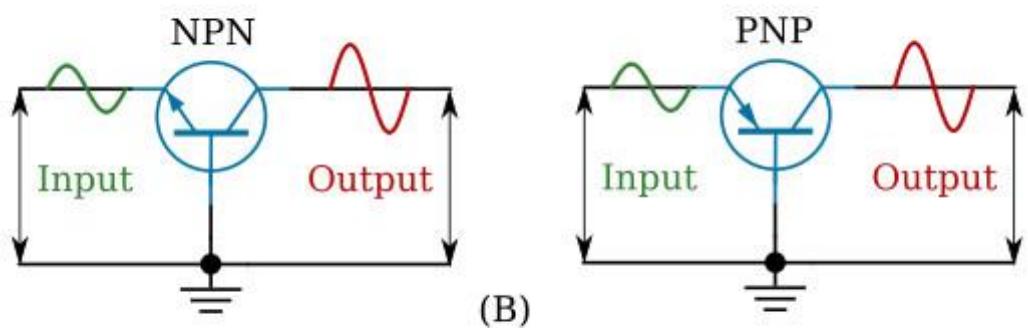

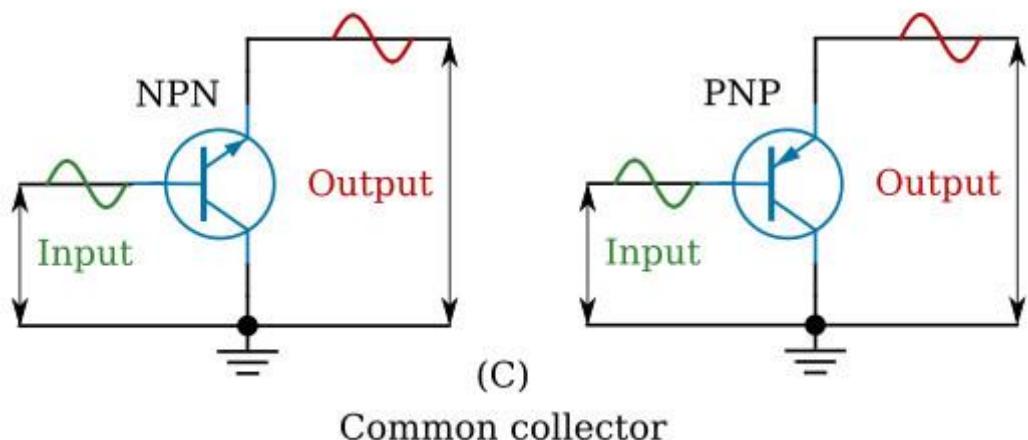

Il existe trois montages qui utilisent le transistor bipolaire seul comme amplificateur. Ils sont obtenus en plaçant une des trois bornes du transistor à la masse (une borne en commun avec l'entrée et la sortie), d'où l'existence de trois montages :

Common emitter

Common base

Common collector

Fig 48 : Montages de base d'un amplificateur à base d'un transistor bipolaire

|                                     | Emetteur commun                           | Base commune       | Collecteur commun  |

|-------------------------------------|-------------------------------------------|--------------------|--------------------|

| Entrée                              | $I_B, V_{BE}$                             | $I_E, V_{EB}$      | $I_B, V_{BC}$      |

| Sortie                              | $I_C, V_{CE}$                             | $I_C, V_{CB}$      | $I_E, V_{EC}$      |

| Gain en tension= $V_{Out}/V_{In}$   | Moyen                                     | Moyen              | Faible $\approx 1$ |

| Gain en courant= $I_{Out}/I_{In}$   | Moyen                                     | Faible $\approx 1$ | Moyen              |

| Gain en puissance= $P_{Out}/P_{In}$ | Elevé                                     | Moyen              | Moyen              |

| Signal de sortie                    | Inversé (décalé $180^\circ$ ) et amplifié | Amplifié           | Amplifié           |

| Impédance d'entrée                  | Moyenne                                   | Faible             | Elevée             |

| Impédance de sortie                 | Moyenne                                   | Elevée             | Faible             |

Ce qui est bon pour l'amplification

Tableau 5 : Comparaison entre les trois types d'amplificateur

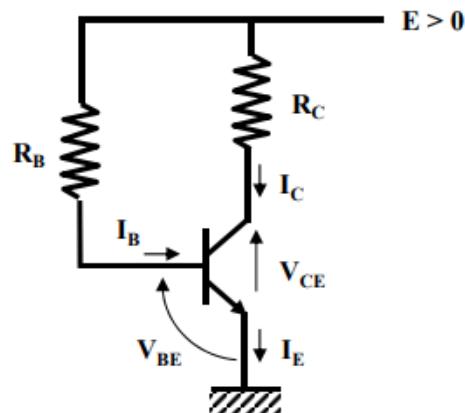

### 1.2.2. Schéma de mesure des caractéristiques.

Le fonctionnement du transistor NPN est décrit par les courbes caractéristiques qui lient les 6 grandeurs électriques  $V_{CE}$ ,  $V_{EB}$ ,  $V_{CB}$  et  $I_C$ ,  $I_E$  et  $I_B$

Les caractéristiques qui suivent sont données pour un montage émetteur commun.

Le schéma le plus simple est le suivant :

Fig 49 : Montage de base émetteur commun

Dans ce schéma, la base est polarisée en direct par la résistance de base  $R_b$  : le potentiel de la base est alors de 0,7V environ, car l'émetteur est à la masse et la jonction base émetteur est l'équivalent d'une diode passante.

Le collecteur est lui polarisé par la résistance de collecteur  $R_c$  de telle manière que la tension du collecteur soit supérieure à la tension de la base : la jonction base collecteur est alors polarisée en inverse.

On polarise donc convenablement le transistor avec une simple alimentation et deux résistances. Dans ce montage, l'entrée est la base et la sortie est le collecteur.

L'entrée est caractérisée par les deux grandeurs  $I_B$  et  $V_{BE}$ , et la sortie par les grandeurs  $I_C$  et  $V_{CE}$ .

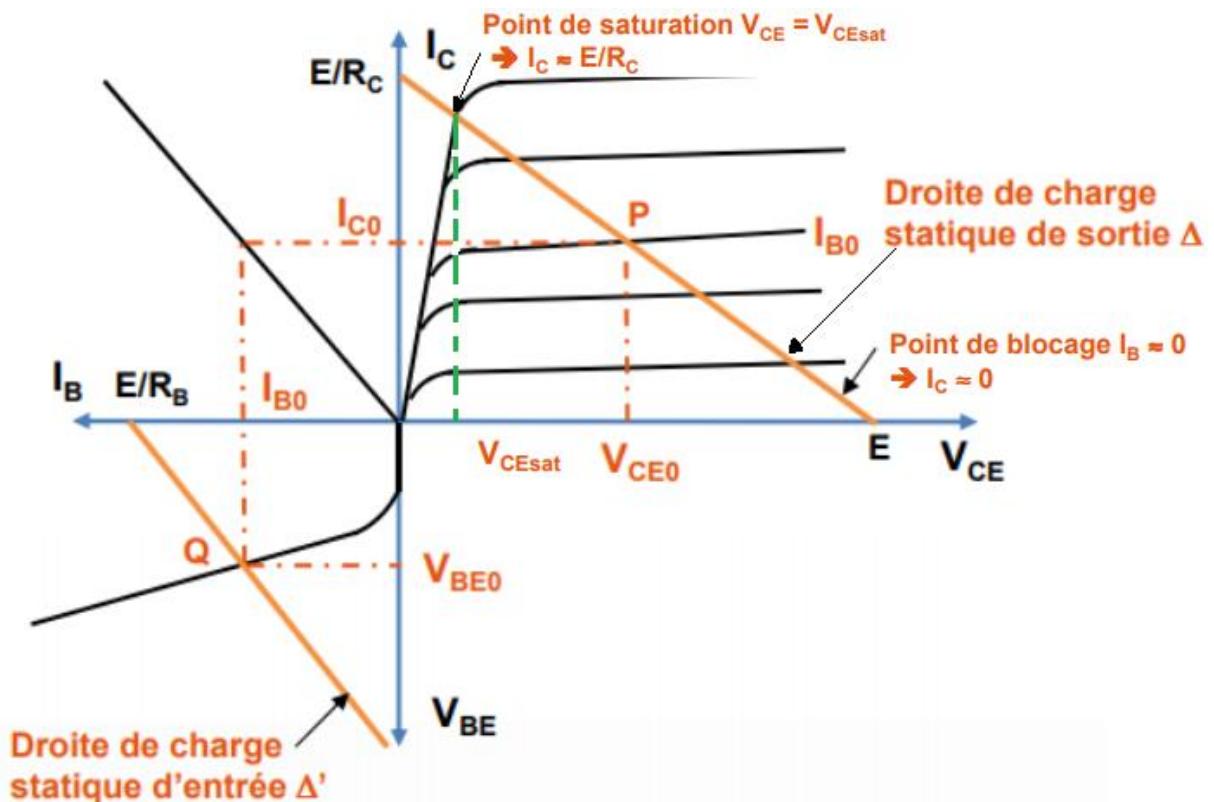

Fig 50 : Caractéristique  $I(V)$  d'un transistor bipolaire

Droite de charge statique de sortie  $\Delta$  :

$$I_C = \frac{E - V_{CE}}{R_C} \quad \rightarrow \text{tracé dans le réseau de caractéristique statique } I_C = f(V_{CE})$$

Droite de charge statique d'entrée  $\Delta'$  :

$$I_B = \frac{E - V_{BE}}{R_B} \quad \rightarrow \text{tracé dans le réseau de caractéristique statique } I_B = f(V_{BE})$$

### Caractéristique d'entrée.

La caractéristique d'entrée du transistor est donnée par la relation  $I_B = f(V_{BE})$ ,  $V_{CE} = \text{cte.}$

Pour une tension  $V_{CE}$  constante, si  $V_{BE}$  varie alors  $I_B$  varie suivant une courbe analogue aux caractéristiques d'une diode. Cela donne la **caractéristique d'entrée  $I_B(V_{BE})$**  :

### Caractéristique de transfert.

La caractéristique de transfert en courant est définie par la relation  $I_C = f(I_B)$  avec  $V_{CE} = \text{cte.}$

On a déjà dit que le courant d'émetteur est proportionnel au courant de base. La caractéristique de transfert est donc une droite ; le transistor est un générateur de courant commandé par un courant.

Le  $\beta$  du transistor va varier grandement en fonction du type de transistor : 5 à 10 pour des transistors de grosse puissance, 30 à 80 pour des transistors de moyenne puissance, et de 100 à 500 pour des transistors de signal.

### Caractéristique de sortie.

La caractéristique de sortie du transistor est définie par la relation  $I_C = f(V_{CE})$  avec  $I_B = \text{cte.}$  En pratique, on donne un réseau de caractéristiques pour plusieurs valeurs de  $I_B$ .

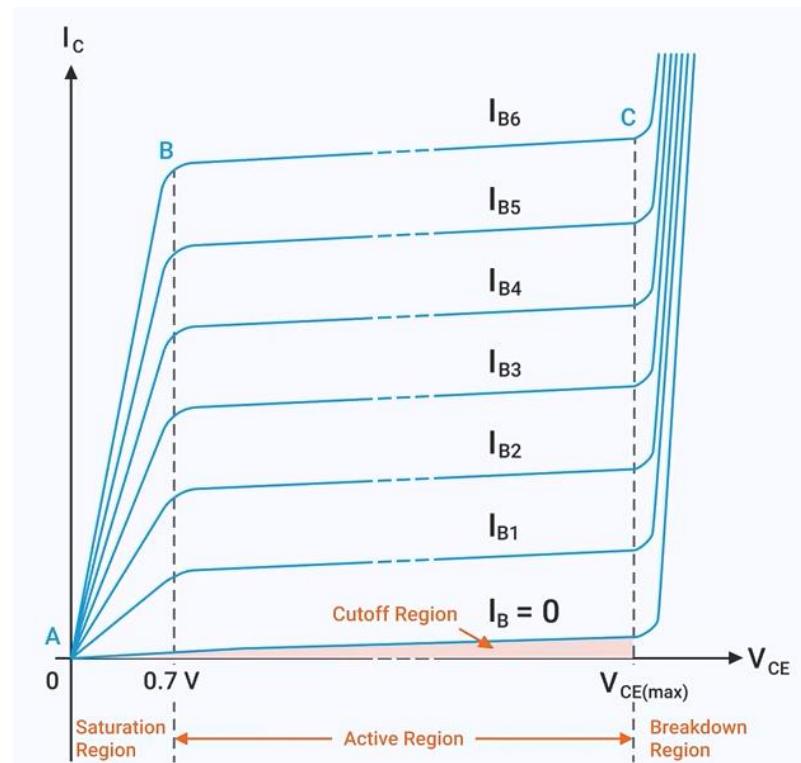

### 1.2.3. Modes de Fonctionnements d'un transistors NPN

Fig 51 : Modes de Fonctionnements d'un transistors NPN à émetteur commun.

#### La région de claquage

C'est quand la valeur de  $I_C$  est très grande

#### La région de coupure (CutOff)

Le transistor fonctionne comme un interrupteur ouvert. Donc  $I_B=0$  et  $I_C=0$

#### La région active

Dans cette région, la jonction base-émetteur est polarisée dans le sens direct, tandis que la jonction base-collecteur est polarisée dans le sens inverse.

On note que : quel que soit  $V_{CE}$  [ $0.7V < V_{CE} < V_{CE(\max)}$ ] il y a presque aucun changement dans  $I_C$  mais il y a un grand effet de  $I_B$  sur  $I_C$ . Donc pour contrôler le courant de sorti  $I_C$  on joue seulement sur  $I_B$  (l'amplification dépend aussi du  $\beta$ ) et c'est comme ça on utilise le transistor comme un **amplificateur**

## La région de saturation

Elle présente une variation linéaire entre  $I_C$  et  $V_{CE}$ . Elle présente deux états ou deux modes de fonctionnement. Dans cette région, le transistor est utilisé comme un **commutateur**

### A. Etat bloqué (état logique est 0) :

- Si la jonction base-émetteur du transistor est polarisé en inverse  $V_{EB}$  ou

- Si la tension  $V_{EB}$  est inférieure à la tension de seuil du transistor, aucun courant ne circule.

Donc on dit « le transistor est **bloqué** » ça veut dire qu'il se comporte comme un interrupteur ouvert et que le collecteur est isolé de l'émetteur.

### B. Etat saturé (état logique est 1)

En saturation, les deux jonctions du transistor conduisent

Le transistor est **saturé** lorsque ses deux jonctions sont en polarisation directe cela est réalisé lorsque la tension au collecteur est inférieure à la tension à la base (en saturation, les électrons du collecteur vont balayer dans la base et on a des électrons entrant de l'émetteur dans la base et comme la région de base est étroite et très légèrement dopée, alors tous les trous libres sont recombinés avec des électrons de telle sorte qu'en saturation, toute la région de la base va être épuisé et effectivement on n'aura plus 2 jonctions PN, on aura simplement un SC saturé d'électrons et le courant  $I_C$  ne dépend pas de  $I_B$ ).

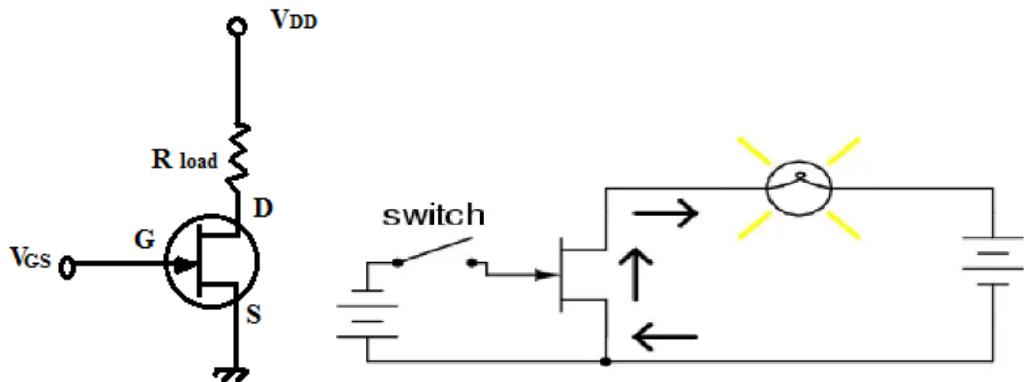

### 1.3. TRANSISTOR NPN EN COMMUTATION

Le transistor NPN peut prendre deux états possibles lors qu'il est utilisé en mode de commutation

Bloqué : il se comporte comme un interrupteur ouvert

Passant et saturé : il se comporte comme un interrupteur fermé

La valeur de  $I_B$  va permettre de choisir le mode de commutation du transistor.

Si  $I_B = 0 \Rightarrow I_C = 0, V_{CE} = V_{CC} \Rightarrow$  le transistor est bloqué

Si  $I_B > I_C/\beta \Rightarrow I_C = I_{C\text{sat}}, V_{CE} \approx 0$  (environ 0.2 V)  $\Rightarrow$  le transistor est saturé

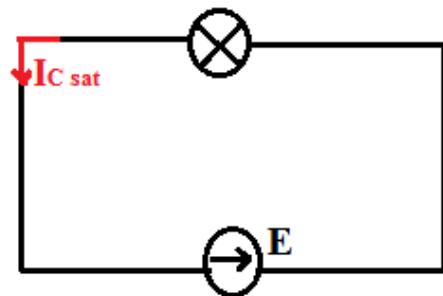

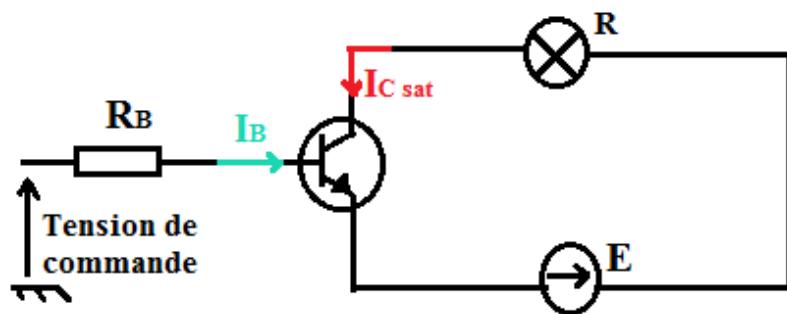

**Exemple :** Si on alimente une lampe avec une alimentation  $E = 12V$ . Dans le circuit il va passer un courant  $I_{C\text{sat}}$

Pour commander cette lampe (Allumer la lampe ou l'éteindre) avec un transistor, on doit réaliser le circuit suivant (voir la figure ci-dessous)

(a)

(b)

Fig 52 : (a) circuit non commandé. (b) circuit commandé par un transistor NPN

Si la tension de commande  $V = 0$   $I_B = 0$  le transistor se comporte comme un interrupteur ouvert et le moteur ne tourne pas

Si  $V = 5V$  et  $V_{EB} \geq 0.7V$  et on mit une résistance  $R_B$  de tels sorte que  $I_B > I_{C\text{ sat}}/\beta$ , le transistor est saturé et se comporte comme un fil et le moteur va tourner

### Calcul de la résistance de base

$$R = 50 \Omega \quad V_{CE\text{ sat}} = 0,2 \text{ V} \quad V_{BE} = 0,7 \text{ V} \quad 200 < \beta < 300 \quad V = 5 \text{ V}$$

❖ Calculer  $I_C$

$$I_C = (E - V_{CE\text{ sat}}) / R = (12 - 0,2) / 50 = 0,236 \text{ A}$$

❖ Calculer  $I_{B\text{ sat}}$

Le courant de base  $I_B$  suffisant pour saturer le transistor est  $I_B > I_C/\beta$ .

$$I_{B\text{ min}} = \frac{I_C}{\beta_{\text{min}}} = \frac{0.236}{200} = 0.00118 = 1.18mA$$

On prend un coefficient de sécurité de  $k= 2$  pour être sûr que le transistor soit bien saturé

:

$$I_{Bsat} = 2 \times I_{B\text{ min}} = 2.36mA$$

❖ Calculer  $R_B$

$$R_B = \frac{V_R}{I_{Bsat}} = \frac{V - V_{BE}}{I_{Bsat}} = \frac{5 - 0.7}{0.00236} = 1.81K\Omega$$

NB : Pour vérifier la saturation d'un transistor, il suffit de mesurer sa tension  $V_{CE}$ . Si elle est presque égale à 0 (et que bien sûr le montage est alimenté et correctement polarisé), le transistor est saturé. Si elle est égale à la tension d'alimentation, le transistor est bloqué. Si le transistor est tout le temps bloqué ou tout le temps saturé, ça veut dire qu'il est défectueux

### **1.4. TRANSISTOR NPN EN AMPLIFICATION**

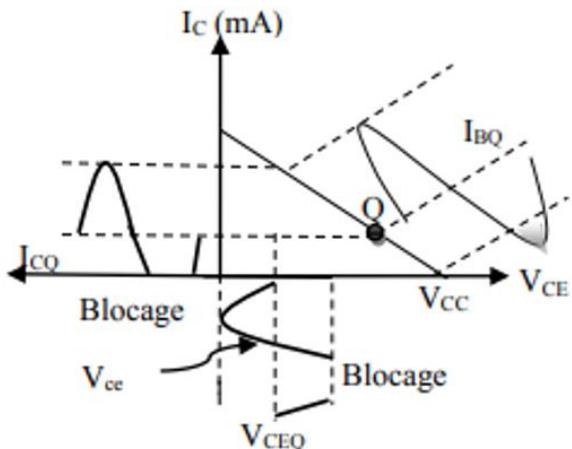

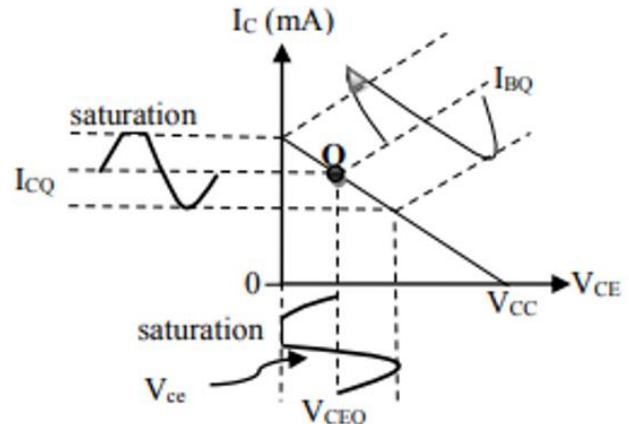

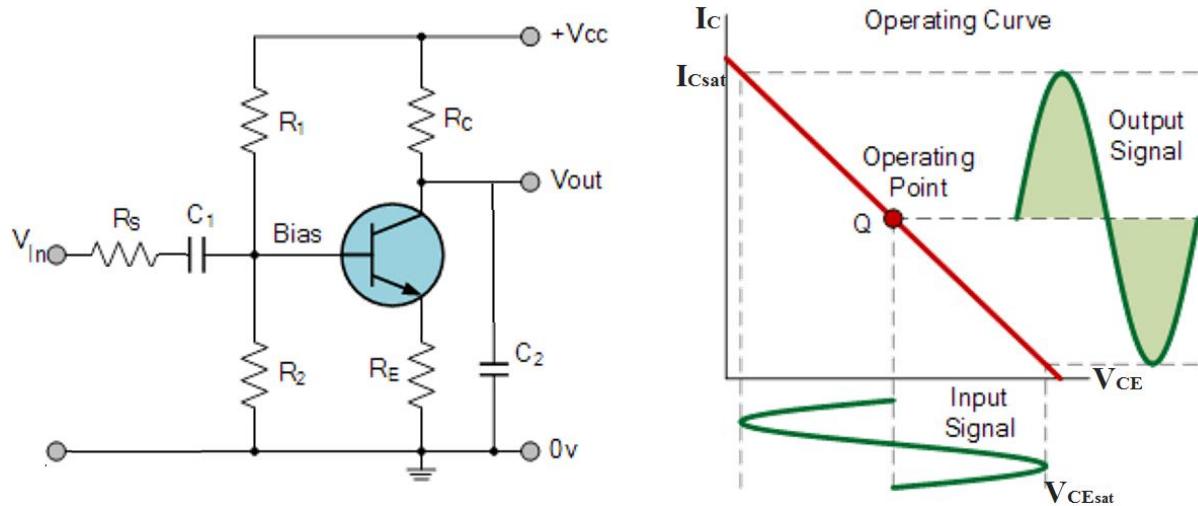

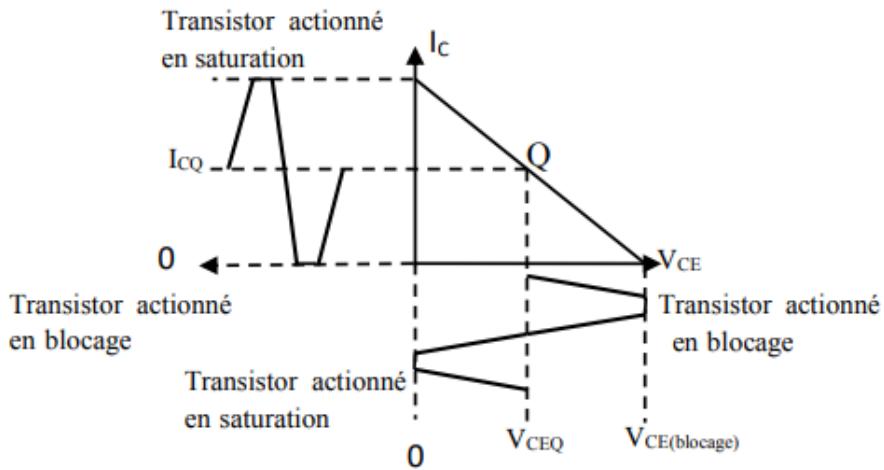

L'emplacement du point (Q) sur la droite de charge peut engendrer l'écrêtage de l'une au l'autre des alternances de la forme d'onde de sortie  $V_{CE}$  tel qu'il est illustré sur la figure 53.

Pour éviter la distorsion à la sortie, il faut limiter la crête maximale de  $V_{CE}$  à  $0.95V_{CC}$  et la crête minimale à  $0.05V_{CC}$  avec un point (Q) en plein centre de la droite de charge

a) transistor activé en blocage

b) transistor activé en saturation

Fig 53 : Transistor actionné en blocage et en saturation

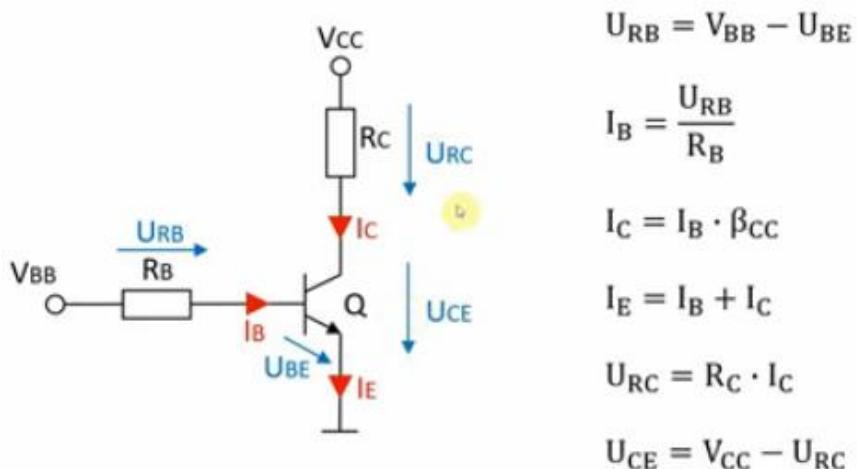

### Détermination du point Q

#### A. Détermination du point N :

À partir de la maille d'entrée on applique la loi des mailles ce qui donne :  $V_{BB} = R_B I_B + V_{BE}$

Le point N est défini par l'intersection de la caractéristique d'entrée du transistor  $V_{BE} = f(I_B)$  et de la droite d'équation  $V_{BE} = V_{BB} - R_B I_B$  appelée droite d'attaque statique.

La connaissance du point  $(V_{BE}, I_B)$  permet la détermination du courant  $I_{C0}$

## B. Détermination du point Q

L'équation de la droite de charge statique est définie, à partir de la maille de sortie, par  $V_{CE}=V_{CC} - R_C I_C$ . L'intersection de cette droite avec la caractéristique de sortie du transistor (correspondant au courant  $I_{B0}$  d'entrée) définit le point de repos en sortie Q caractérisé par  $I_{C0}$  et  $V_{CEO}$ .

On classe les amplificateurs de puissances suivant le temps de conduction des composants actifs (leurs points de fonctionnements Q nous permet de contrôler le point de démarrage et d'arrêt du signale) en 4 principaux classes

### Classe A

L'amplificateur classe A est un amplificateur à émetteur commun qui est polarisé de façon à ce qu'il fonctionne dans la région linéaire pendant toute la période du signale d'entrée. La forme d'onde de la tension de sortie est donc une réplique amplifiée de celle de l'entée. Un amplificateur classe A peut-être avec ou sans inversion.

Comme le transistor conduit pour le cycle complet  $360^\circ$  de l'entrée ça va générer beaucoup de dissipation thermique ce qui réduit le rendement de l'amplificateur (25%). Ce dernier est linéaire et il présente très peu de distorsions parce que le transistor ne s'éteint jamais pendant le cycle du signal. Il est utilisé en audiofréquence

L'amplificateur présenté dans la figure est un amplificateur à émetteur commun polarisé de façon à ce qu'il fonctionne dans la région active (son point de fonctionnement se situe dans le milieu de la droite de charge statique) pendant toute la durée du cycle du signal d'entrée. Dans ce mode de fonctionnement, l'amplificateur ne passe pas ni en blocage ni en saturation.

Fig 54 : Circuit et caractéristique  $I(V)$  d'un amplificateur classe A

Le transistor NPN dans la figure 54 est polarisé par un diviseur de tension, avec une source de tension (courant alternatif), couplée à la base par le condensateur C1 et dont la charge est couplée au collecteur par le condensateur C2. Les condensateurs de couplage bloquent les courants continus et empêchent la résistance de la source RS et la résistance de la charge de changer les tensions continues de polarisation à la base et ou collecteur.

La tension de la source sinusoïdale fait osciller la tension à la base au-dessus et au-dessous de son niveau de polarisation, par conséquent, la variation en courant à la base produit une variation plus grande en courant au collecteur à cause du gain en courant du transistor (de même pour la tension).

Les résistances de base  $R_B$  et d'émetteur  $R_E$  sont utilisées pour définir le courant de base  $I_B$  et stabiliser le point de fonctionnement (Q-point).

Lorsque le signal d'entrée est trop grand, l'amplificateur est actionné en blocage et en saturation, causant un écrêtage du signal

L'amplificateur de classe A est utilisé dans les applications où la qualité sonore prime sur l'efficacité énergétique comme les préamplificateurs microphoniques

Fig 55: Ecrêtage du signal de sortie lors le blocage et la saturation

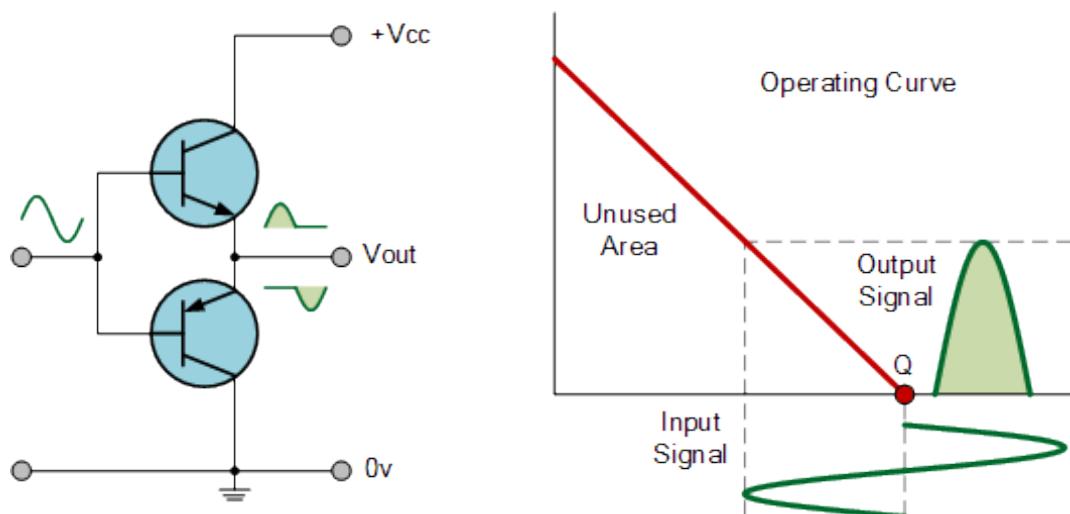

### Classe B

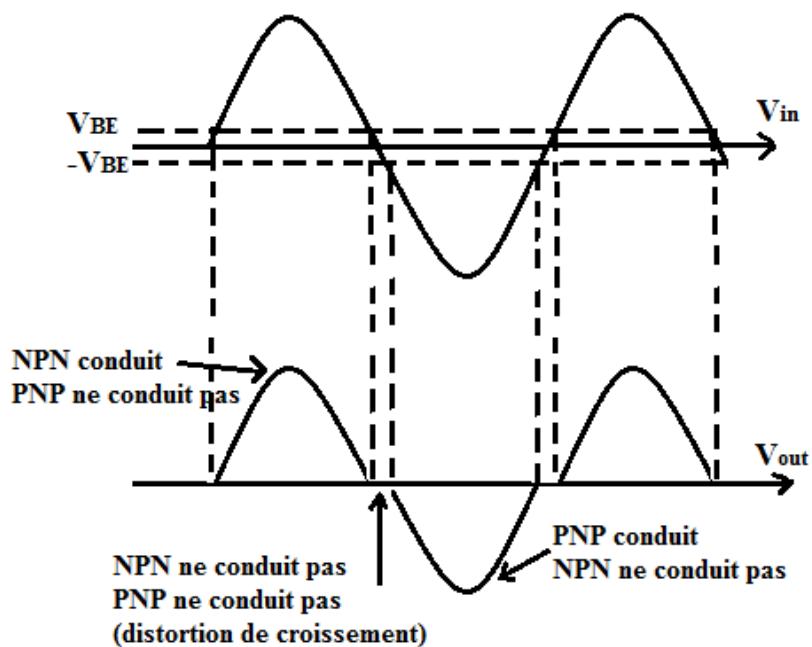

Il est conçu pour améliorer l'efficacité énergétique par rapport à un amplificateur de classe A. Il se compose d'une paire de transistors complémentaires NPN et PNP, chaque un des transistors conduit durant une demi période du signal d'entrée (le NPN amplifie l'alternance positive du signal d'entrée et le PNP amplifie l'alternance négative du signal d'entrée). Cela réduit la consommation d'énergie et augmente son rendement jusqu'à 60%. Il n'est pas linéaire donc il présente des distorsions dans le signal lorsque il passe par zéro, car les transistors ne se conduisent pas simultanément à ce point. Lorsqu'un amplificateur est polarisé au point de blocage, de façon à opérer dans la région linéaire pour 180° du cycle d'entrée et qu'il est en blocage pour l'autre 180°, c'est un amplificateur classe B.

Fig 56: Fonctionnement d'un amplificateur PUSH-PULL en classe B

L'amplificateur Classe B est polarisé au point de blocage de façon à ce que  $I_{CQ} = 0$  et que  $V_{CEQ} = V_{CE(\text{blocage})}$ . Lorsque le signal actionne le transistor en état de conduction l'amplificateur sort de l'état de blocage et fonctionne dans sa région linéaire.

Lorsque la tension de polarisation  $V_{CC}$  à la base est nulle, les deux transistors ne conduisent pas. Pour cette raison, il existe un intervalle de temps entre les alternances positives et négatives de l'entrée pendant lequel aucun des transistors ne conduit. La distorsion qui en résulte dans la forme d'onde de sortie est bien connue : on l'appelle la distorsion de croisement.

Fig 57: Illustration de la distorsion de croisement

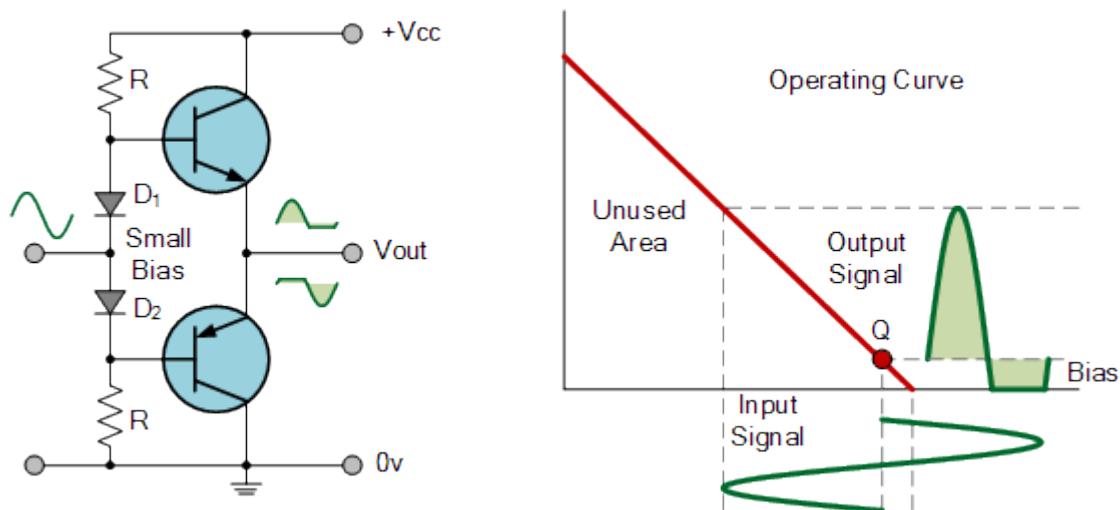

### Classe AB

Les amplificateurs classe AB combinent les avantages des classes A et B pour offrir une meilleure efficacité énergétique que les amplificateurs de classe A, tout en minimisant la distorsion de croisement inhérente aux amplificateurs de classe B. La plupart des amplificateurs audio courants sont amplificateurs AB comme les amplificateurs des Smartphones et des lecteurs audio premium, les systèmes home cinéma, les amplificateurs de studio polyvalents et les systèmes de sonorisation pour concerts ...etc

- Dans un amplificateur de classe AB, les transistors sont polarisés de manière à conduire plus de la moitié du cycle du signal d'entrée (entre 180° et 360° ça dépend de la polarisation de la base des transistors par les diodes), mais pas la totalité comme dans un amplificateur de classe

A. Cela signifie qu'il y a une légère zone de chevauchement où les deux transistors conduisent simultanément.

□ Pour réduire la distorsion de croisement, on utilise des diodes de polarisation ou des circuits de polarisation active. Ces diodes créent une légère tension de décalage (environ 0.7V pour chaque diode en silicium) ce qui permet aux transistors de commencer à conduire avant que le signal d'entrée ne dépasse ce seuil. Donc chaque transistor commence à conduire légèrement avant que l'autre ne s'éteigne, ce qui élimine la distorsion de croisement présente dans les amplificateurs de classe B.

Fig 58 : Circuit et caractéristique  $I(V)$  d'un amplificateur classe AB

Lorsque  $V_{IN} = 0$ , un faible courant constant traverse les diodes D<sub>1</sub> et D<sub>2</sub> et les transistors (typiquement quelques dizaines de mA) fourni par la source de courant  $V_{CC}$

□ Lorsqu'on augmente le signal d'entrée (l'alternance positive), la tension  $V_{IN}$  s'ajoute à la tension de polarisation du transistor NPN et la tension de la diode D<sub>1</sub>.  $V_S = V_{IN} + V_{D1} - V_{BE1}$

Donc pour  $V_{IN}=0$ ,  $V_D= 0.7$  et  $V_{BE1}=0.7$  (tension de seuil du TR1)  $\rightarrow V_S=V_{IN}$  et donc on a supprimé les distorsions. Le transistor NPN conduit de plus en plus avec l'augmentation du signal  $V_{IN}$ . Par contre le transistor PNP se rapproche progressivement du cut-off, mais sans l'atteindre complètement.

- Lors l'alternance négative la tension de sortie  $V_S$  devient  $V_S = V_{IN} - V_{D2} - V_{BE2}$

Donc pour  $V_{IN}=0$ ,  $V_{D2} = -0.7$  et  $V_{BE2}=0.7$  (tension de seuil du TR2)  $\rightarrow V_S = V_{IN}$  et donc on a supprimé les distorsions de croisement. Le transistor PNP conduit de plus en plus avec l'augmentation du signal  $V_{IN}$ . Par contre le transistor NPN se rapproche progressivement à la région de coupure (Cut-Off) mais sans l'atteindre complètement.

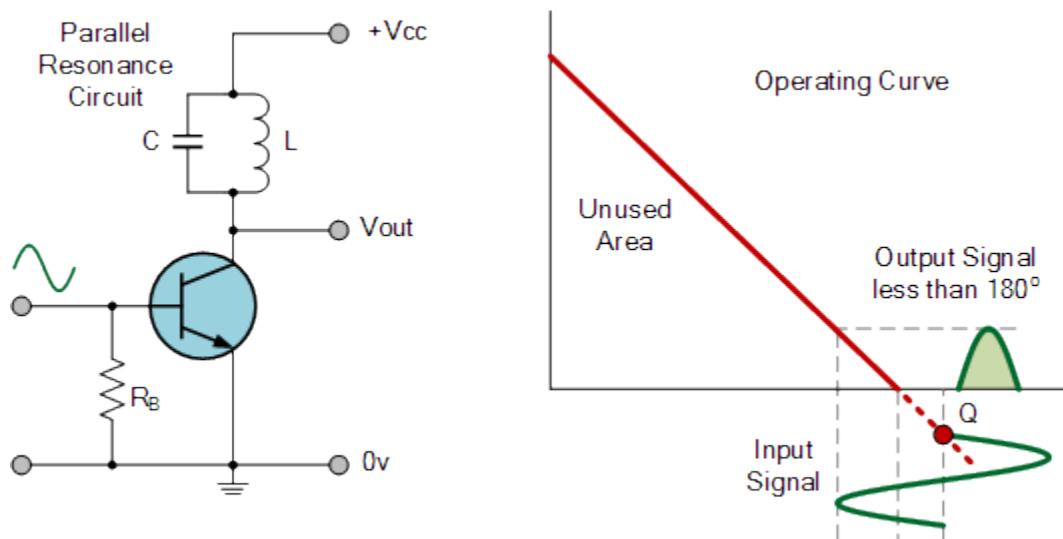

### Classe C

Les amplificateurs classe C sont des amplificateurs de très haute efficacité énergétique, souvent supérieure à 80% car le transistor conduit pendant moins de la moitié du cycle du signal d'entrée (donc il utilise peu d'énergie). Pour réaliser ce type d'amplificateur, le transistor doit être polarisé de manière à être bloqué la plupart du temps. Ces amplificateurs sont inadaptés pour des applications audio mais ils sont idéaux pour les applications où la distorsion élevée est acceptable et peut être facilement filtrée comme dans les émetteurs RF, les oscillateurs et les multiplicateurs de fréquence.

Fig 59 : Circuit et caractéristique  $I(V)$  d'un amplificateur classe C

Dans le circuit présenté dans la figure le point de repos (qui est déterminé par la tension de polarisation appliquée à la base du transistor lors l'absence de signal d'entrée) doit être fixé en dessous de la tension de seuil du transistor qui est 0.7 volts. Autrement dire, la tension de polarisation est inférieure à 0,7V. elle peut être 0V ou même négative

La plupart du temps, le transistor est bloqué et  $IC=0$  sauf lorsque le signal d'entrée dépasse 0,7V il devient conducteur et on voit des impulsions positives dans la sortie.

Le circuit LC lié au collecteur est accordé à la fréquence du signal d'entrée. Il est utilisé pour reconstituer la forme d'onde sinusoïdale à partir des impulsions.

Une fois ce circuit est excité par une impulsion, il produit des oscillations à sa fréquence de résonance. Ceux-ci seront progressivement amortis jusqu'à l'impulsion suivante

Voici une comparaison entre des amplificateurs de classe A, B, AB et C :

|                              | Classe A                                          | Classe B                                           | Classe AB                                            | Classe C                                        |

|------------------------------|---------------------------------------------------|----------------------------------------------------|------------------------------------------------------|-------------------------------------------------|

| Angle de conduction          | 360°                                              | 180°                                               | Entre 180° et 360°                                   | Moins de 180°                                   |

| polarisation                 | Le point de repos est au milieu de la zone active | Le point de repos est juste au seuil de conduction | Le point de repos est légèrement au-dessus du seuil. | Le point de repos est en-dessous du seuil.      |

| Linéarité et distorsion      | Excellent linéarité, très faible distorsion       | Distorsion de croisement significative             | Bonne linéarité, faible distorsion                   | Forte distorsion, nécessite un circuit résonant |

| Efficacité énergétique       | Faible (typiquement 25-30%)                       | Moyenne à élevée (jusqu'à 75%)                     | Moyenne (50-70%)                                     | Très élevée (jusqu'à 90% et plus)               |

| Qualité sonore               | Excellent                                         | Moyenne à bonne                                    | Très bonne                                           | Non adaptée à l'audio                           |

| Rendement à faible puissance | Constant mais faible                              | Faible                                             | Meilleur que B                                       | Élevé, mais non linéaire                        |

Tableau 6 : Comparaison entre les classes d'amplificateur

## 2. LES TRANSISTORS A EFFET DE CHAMP (FIELD EFFECT TRANSISTORS FET)

Le transistor à effet de champ (FET - Field Effect Transistor) est un transistor unipolaire qui utilise le champ électrique pour contrôler la conductivité d'un « canal » dans un matériau semi-conducteur. Il possède trois électrodes qui se nomment la source (S), le drain (D) et la grille (G). La tension appliquée à la grille contrôle le courant circulant dans le canal source-drain. Aucun courant ne traverse l'électrode de grille, donc l'impédance d'entrée du FET est extrêmement grande (de l'ordre de  $10^{10}$  à  $10^{15}$   $\Omega$ ). La grande impédance d'entrée du FET en fait un excellent choix pour les entrées d'amplificateur. Le transistor FET concurrence également le transistor bipolaire dans d'autres domaines d'applications, tels que l'électronique numérique. Il existe plusieurs sortes de transistors à effet de champ, les deux familles les plus connues sont : le FET à jonction (JFET) et le FET à semi-conducteur à oxyde métallique (MOSFET). Ces deux familles diffèrent par la manière dont le contact de grille est établi sur le canal source-drain.

Dans le JFET, le contact grille-canal est une jonction PN polarisée en inverse. Tous les JFET sont des dispositifs en mode d'appauvrissement : ils sont activés lorsque la polarisation de grille est nulle ( $V_{GS} = 0$ ).

Par contre dans le MOSFET, la grille est séparée du canal par une fine couche d'oxyde isolant. Les MOSFET sont fabriqués à la fois en mode d'appauvrissement (On lorsque la grille est polarisée nulle,  $V_{GS} = 0$ ) et en mode d'enrichissement (Off avec une grille polarisée zéro).

### 2.1. LES TRANSISTORS JFET

JFET (FET à jonction ou Junction Field-Effect Transistor) est un transistor commandé en tension (la tension à la grille contrôle le courant principal  $I_D$ ). Le courant principal est créé soit par les électrons (JFET de type canal N), soit par trous (transistor JFET de type canal P). Par conséquent, JFET est un composant unipolaire.

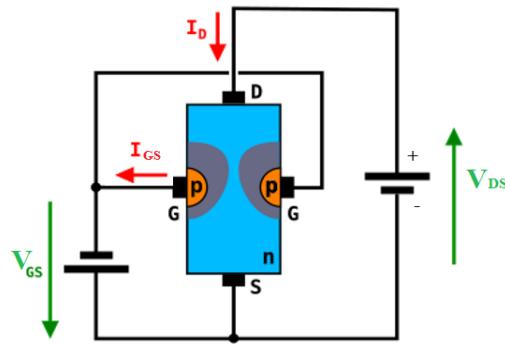

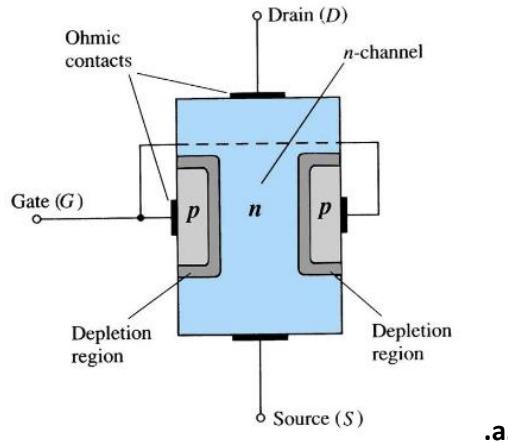

#### 2.1.1. JFET à canal N

□ Un JFET à canal n est constitué d'un canal de SC de type N entre deux régions de SC de type P qui forment la grille. La présence de deux matériaux de type P forme deux jonctions PN à l'intérieur du transistor JFET.

- La tension  $V_{DS}$  qui alimente ce transistor est positive (drain plus positif que la source), donc le courant  $I_D$  circule de la source au drain.

- La tension de grille  $V_{GS}$  qui contrôle ce courant doit être négative pour pouvoir moduler la largeur du canal

- Le canal se rétrécit quand  $V_{GS}$  devient plus négative pour cela le courant  $I_{DS}$  diminue quand  $|V_{GS}|$  augmente

Fig 60 : Polarisation d'un JFET à canal N

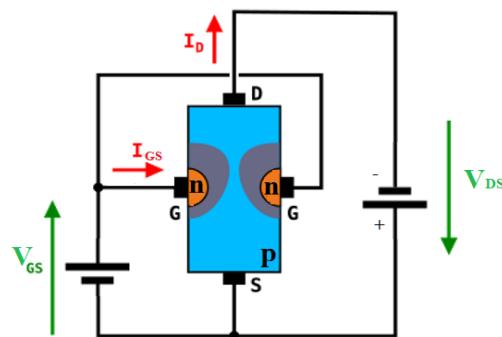

### 2.1.2. JFET à canal P

- Un JFET à canal P est constitué d'un canal de SC de type P entre deux régions de SC de type N qui forment la grille. La présence de deux matériaux de type N forme deux jonctions PN à l'intérieur du transistor JFET.

- La tension  $V_{DS}$  qui alimente ce transistor est négative (drain plus négatif que la source), donc le courant  $I_D$  circule du drain vers la source (sens opposé au JFET canal N)

- La tension de grille  $V_{GS}$  qui contrôle ce courant doit être positive pour pouvoir moduler la largeur du canal

- Le canal se rétrécit quand  $V_{GS}$  devient plus positive pour cela le courant  $I_{DS}$  diminue quand  $|V_{GS}|$  augmente

Fig 61 : Polarisation d'un JFET à canal P

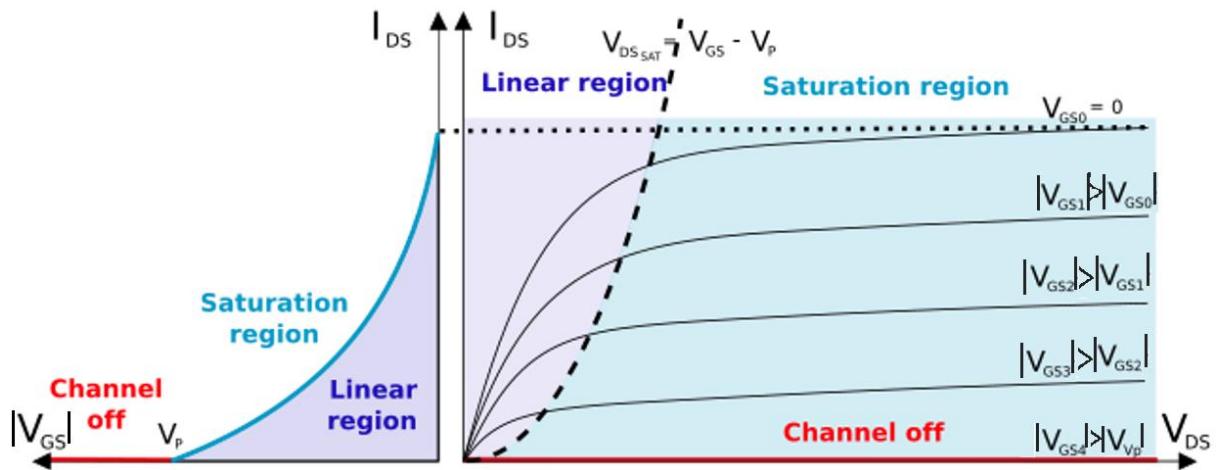

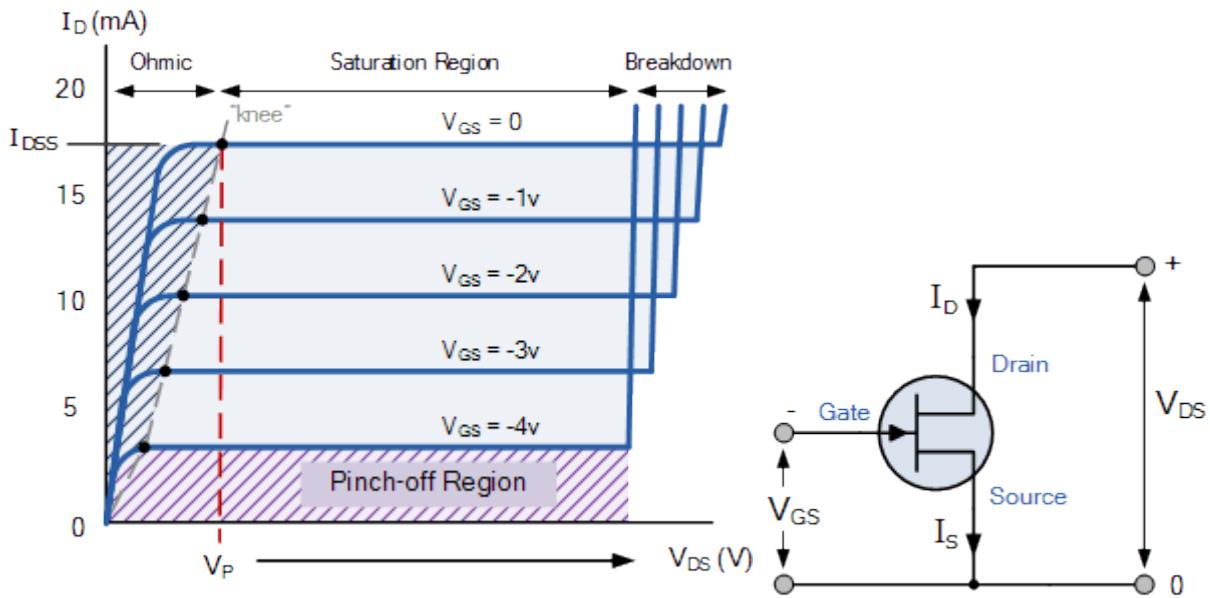

Fig 62: Caractéristiques d'un transistor JFET

IDSS : Courant de drain maximal lorsque  $V_{GS} = 0V$

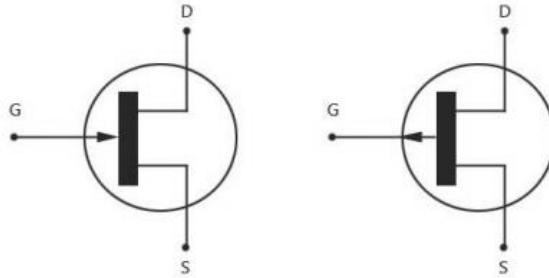

### 2.1.3. SYMBOLE

Fig 63: JFET à canal N (à gauche) JFET à canal P (à droite)

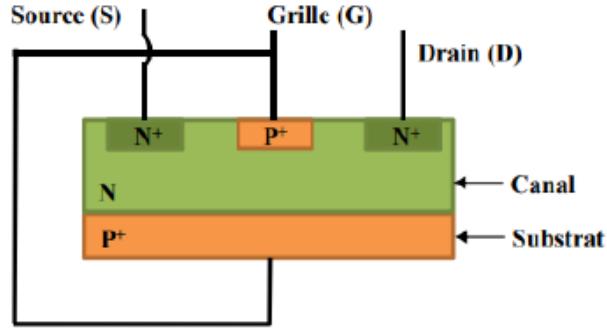

### 2.1.4. STRUCTURE

Un JFET est constitué d'un

**Canal** : représente la barre de SC type N ou type P avec deux contacts (source et drain) aux extrémités.

**Drain (D)** : Terminal où le courant sort du JFET (les porteurs de charges majoritaires sortent du composant).

**Source (S)** : Terminal où le courant entre dans le JFET (les porteurs de charges majoritaires entrent dans le composant).

**Grille (G) :** Son dopage est opposé au canal. C'est une électrode de commande où une tension est appliquée pour contrôler le courant entre le drain et la source

Fig 64 : Structure d'un JFET à canal N

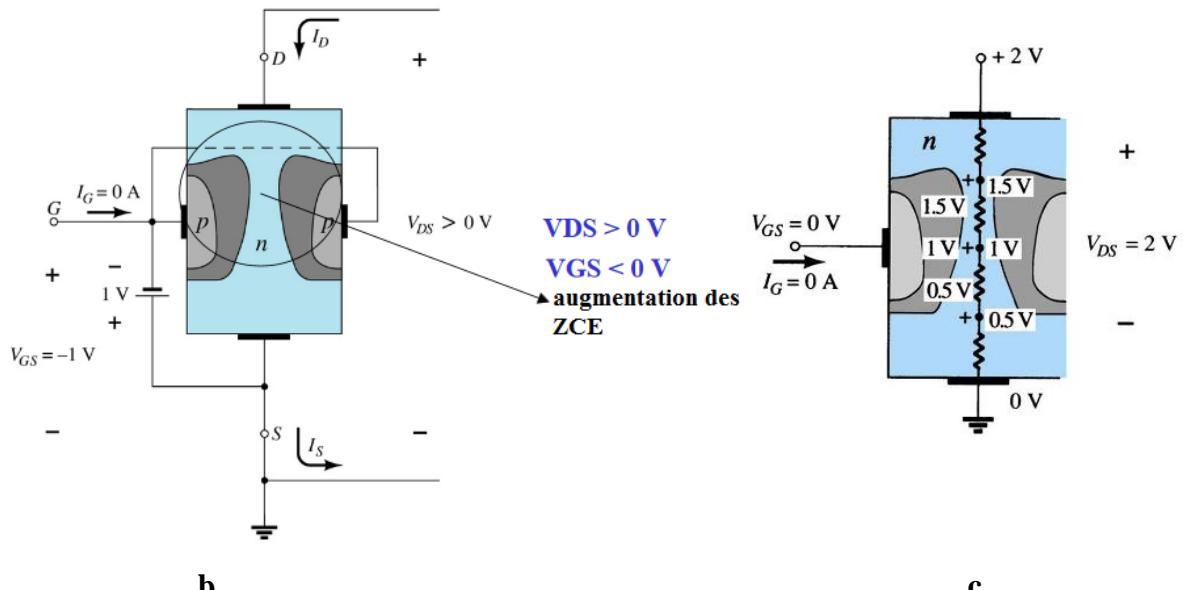

### 2.1.5. PRINCIPE DE FONCTIONNEMENT

Dans le cas d'un transistor JFET à canal N, il existe deux régions d'appauvrissement formées à deux jonctions PN. On sait qu'il n'y a pas de porteurs de charges libres dans les régions ZCE. Donc elles ne nous aideront pas dans la conduction (Fig 65.a).

Si on augmente la largeur des régions d'appauvrissement, la largeur du canal N diminuera et de ce fait, il y aura une obstruction dans le flux d'électrons vers le drain. On peut contrôler la largeur des ZCE à l'aide de la grille. En d'autres termes, afin de contrôler le courant  $I_D$ , on utilise la différence de potentiel entre la grille et la source (si  $V_{GS} > 0$ , la jonction PN devient polarisée en direct et sa largeur n'augmentera pas avec l'augmentation de  $V_{GS}$ . Donc, on ne pourra pas contrôler le courant  $I_D$  par  $V_{GS}$ . C'est pourquoi la polarisation doit être  $V_{GS} \leq 0$ ) et c'est pourquoi le transistor JFET est un dispositif commandé en tension.

- Lorsqu'on connecte le drain et la source à une différence de potentiel  $V_{DS}$  supérieure à 0 et la grille à la différence de potentiel  $V_{GS} = 0$  (voir Fig 65.b), les électrons du transistor JFET à canal N se déplacent vers le haut et le courant drain-source  $I_D$  continue d'augmenter avec l'augmentation de  $V_{DS}$  jusqu'on atteint une tension de pincement  $V_P = V_{DS}$ . C'est la saturation  $I_D = I_{DS} = \text{constant}$

- Si on applique une tension  $V_{GS}$  ( $V_{GS} < 0V$  pour canal N,  $V_{GS} > 0V$  pour canal P), la largeur des régions d'appauvrissement augmentera comme indiquer dans la Fig. ce qui diminue la largeur effective du canal et augmente la résistance du canal. Donc le courant  $I_D$  diminue

- Si on continue d'augmenter  $V_{GS}$  on arrive à une certaine tension de grille négative (tension de pincement  $V_P$ ) où le canal est presque fermé. Le courant drain-source est minimal mais non nul.

Fig 65 : Polarisation d'JFET .a)  $V_{DS}= 0\text{V}$  .b)  $V_{DS}>0$  et  $V_{GS}<0$  .c) résistance du canal

NB:

1. Pour un JFET à canal N : Pour  $V_{GS} = 0$ , la zone de déplétion est plus élargie côté drain que côté source, parce que  $V_{DS}$  est positive (le potentiel appliqué du côté drain est supérieur à celui du côté source  $V_D > V_S$ ). Cela conduit à un "pincement" progressif du canal près du drain et à la saturation lorsqu'on atteint la tension de pincement  $V_P$ .

2. Dans ce cas,  $V_{GS}$  est négatif et  $V_{DS}$  est inférieur à la différence de potentiel appliquée dans le premier cas (le but ici est d'atteindre à la saturation avec une tension

inférieure à  $V_{DS}$  appliqué dans le premier cas). Si on rendre  $V_{GS}$  plus négatif, la largeur des régions de déplétion augmentera jusqu'à ce qu'elles presque se touchent.

Le courant  $I_D$  cessera d'augmenter et deviendra constant même si on augmente  $V_{DS}$  c'est le phénomène de saturation

3. Ces deux régions d'appauvrissement ne se toucheront jamais car si elles le font, il n'y aura pas de courant circulant dans le drain et la source  $I_D = 0$  et donc  $V_D = 0$ . Si  $V_D = 0$ , cela signifie que le côté N et le côté P sont connectés à 0 Volt et cela signifie que la jonction PN n'est plus polarisée en inverse et donc la largeur des régions d'appauvrissement n'augmentera pas.

4. Donc, le canal peut être fermé dans l'un des cas suivants :

- La tension de grille  $V_{GS} = 0$  et  $V_{DS}$  augmente à partir de zéro.

- La tension  $V_{DS} = 0$  et  $V_{GS}$  diminue négativement à partir de zéro.

- $V_{DS}$  et  $V_{GS}$  varient.

### **2.1.6. CARACTERISTIQUES ELECTRIQUE ET REGIMES DE FONCTIONNEMENT**

**a. Caractéristique d'entrée :** Les transistor JFET est toujours utilisé avec des tensions  $V_{GS}$  négatives et inférieures à la tension de claquage inverse. La caractéristique d'entrée de ce transistor est celle d'une diode polarisée en inverse. On a donc toujours :  $I_G = 0$ .

**b. Caractéristique de sortie :** La caractéristique de sortie d'un JFET à canal N est donnée par le réseau des courbes  $I_D = f(V_{DS})$  à différentes valeurs de  $V_{GS} \leq 0$ . Ce réseau est caractérisé par quatre régions utiles :

#### **Régime bloqué**

Il se produit lorsque la tension de grille-source  $V_{GS}$  est suffisamment négative pour fermer complètement le canal de conduction ce qui empêche le passage des porteurs de charge. Ainsi le courant  $I_D$  est pratiquement nul (en réalité un très faible courant de fuite peut exister). Dans la région de coupure le canal est contrôlé par la tension  $V_{GS} < V_P$  par contre  $V_{DS}$  (qui est  $< V_{GS} - V_P$ ) a un effet négligeable

Ce régime est utilisé pour des applications de commutation, où le JFET agit comme un interrupteur ouvert

## Régime ohmique

Le régime ohmique, également appelé régime linéaire parce que le courant du drain  $I_D$  varie linéairement avec la tension  $V_{DS}$ . C'est lorsque la tension  $V_{GS} > V_P$  (tension de pincement)

Le canal dans ce régime se comporte comme une résistance contrôlée par la tension  $V_{GS}$  parce que la section du canal varie en fonction d'elle. Le courant varie de 0 à une valeur de

$$\text{saturation } I_{DSS} \text{ et } R_{DS} = \frac{R_{DS[V_{GS}=0]}}{1 - \frac{V_{GS}}{V_P}}$$

On utilise le JFET dans cet intervalle dans les multiplieurs analogiques et les résistances contrôlées en tension.

## Régime de saturation

Dans ce régime la tension  $V_{GS} > V_P$ , le canal est pincé du côté du drain et le courant de drain  $I_D$  est presque constant et indépendant de la tension  $V_{DS}$  tant qu'elle reste dans la plage de saturation ( $V_{DS} \geq V_{GS} - V_P$ )

Le JFET agit comme une source de courant contrôlée par la tension de la grille. Ce comportement est précieux pour les applications d'amplification, car le gain en tension est élevé et le courant de drain peut être ajusté par  $V_{GS}$  avec une faible dépendance à  $V_{DS}$

$$I_D = I_{DSS} * (1 - V_{GS}/V_P)^2$$

$I_D$  : Courant de drain

$I_{DSS}$  : courant maximal qui peut circuler dans le canal quand  $V_{GS} = 0$ .

$V_{GS}$  : Tension grille-source

$V_P$  : Tension de pincement (c'est la tension grille-source à laquelle le canal est complètement fermé)

Quand  $V_{GS}$  augmente (en valeur négative), ce terme diminue, réduisant ainsi le courant  $I_D$ . Quand  $V_{GS} = V_P$ , le courant  $I_D$  devient théoriquement nul.

## Régime de claquage

Le régime de claquage survient lorsque la tension drain-source  $V_{DS}$  dépasse une valeur critique, provoquant une augmentation soudaine et incontrôlée du courant de drain.

$V_{\text{claquage}}$  : C'est la tension  $V_{\text{DS}}$  maximale que le JFET peut supporter avant d'entrer en claquage

Le claquage peut endommager irréversiblement le dispositif s'il n'est pas limité rapidement

Fig 66 :Régimes de fonctionnement d'un JFET

### 2.1.7. DOMAINE D'APPLICATION

Les JFETs sont utilisés dans diverses applications en raison de leurs caractéristiques uniques, telles que leur faible consommation d'énergie, leur impédance d'entrée élevée et leur faible bruit et leur capacité à fonctionner à des fréquences élevées.

En pratique, on utilise le JFET dans deux modes bien distincts :

- En zone linéaire où il sert de résistance commandée en tension et il peut être utilisé comme commutateur analogique pour contrôler le passage ou l'arrêt de signaux analogiques

- En zone de saturation où il peut être considéré comme un générateur de courant commandé par une tension

#### A. LES INTERRUPEURS ANALOGIQUES

Les interrupteurs analogiques sont largement utilisés dans les circuits électroniques pour commuter des signaux audio, vidéo, de capteurs et d'autres signaux analogiques. Ils peuvent

être utilisés pour multiplexer plusieurs signaux vers une seule voie de traitement. Il existe différents types d'interrupteurs analogiques, ils diffèrent par leurs applications préférentielles et les exigences spécifiques de ces applications comme la précision, la consommation d'énergie, la linéarité et la puissance de commutation. Les commutateurs JFET sont appréciés dans les applications où l'impédance d'entrée élevé, la faible consommation d'énergie et la linéarité sont des critères indispensables comme dans les préamplificateurs audio, les microphones, les amplificateurs RF et les filtres analogiques de hautes précision

Fig 67 : Interrupteur analogique à base d'un JFET

#### ***Etat ouvert (coupure)***

Lorsque le signal de commande  $V_{GS}$  est suffisamment négative ( $V_{GS} < V_P$  pour N-JFET) ou suffisamment positif ( $V_{GS} > V_P$  pour P-JFET), le canal se pince ce qui empêche le passage du courant  $I_D$  entre le drain et la source. La tension de sortie au drain  $V_D$  monte proche de  $V_{DD}$

#### ***Etat fermé (conduction)***

C'est lorsque  $V_{GS}=0$  ou légèrement négative (pour N-JFET) ou légèrement positive (pour P-JFET). Le JFET est en mode ohmique c.à.d. le canal est ouvert. La tension de sortie  $V_D$  chute et il y a une transmission du signal analogique

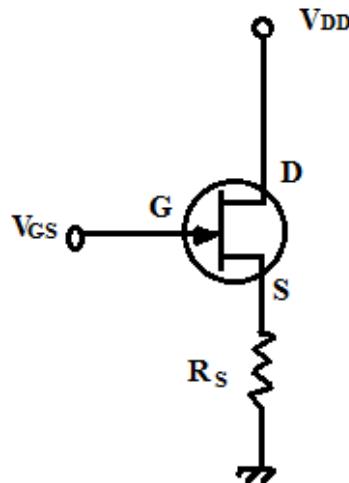

### **B. RESISTANCE CONTRÔLEE PAR TENSION**

Les circuits qui contrôlent leur résistance par une tension externe sont utilisés dans de nombreux domaines tels que : dans les atténuateurs variables qui sont utilisés dans les équipements de test et mesure et dans les circuits audio pour contrôler le volume audio, dans les oscillateurs pour modifier la fréquence de sortie ou modifier la fréquence de coupure des

filtres analogiques, ils sont également essentiels pour contrôler le gain des amplificateurs et dans les capteurs

Fig 68 : Le JFET pour contrôler la résistance

$R_s$  est la résistance de polarisation elle fournit une auto-polarisation au JFET (la chute tension crée au borne la résistance  $R_s$  lors la circulation du courant  $I_D$  est égale à la tension grille-source ( $V_{GS}$ ) du JFET, car la grille est à un potentiel de 0V) et elle aide à stabiliser son point de fonctionnement (si on augmente  $I_D$ , la tension aux bornes de  $R_s$  augmente ce qui rend  $V_{GS}$  plus négative, et donc réduire le courant de drain. Le JFET atteint un point d'équilibre où le courant de drain et la tension  $V_{GS}$  se stabilisent.)

Lorsque  $V_{GS}$  est proche ou égale à 0 la résistance  $R_{DS}$  est faible (typiquement quelques dizaines d'ohms).

Si on augmente  $|V_{GS}|$ , le canal se rétrécit et  $R_{DS}$  augmente

Si  $V_{GS}$  atteint la tension de pincement, le canal est complètement pincé et  $R_{DS}$  devient très élevé (plusieurs mégohms).

### C. SOURCE DE COURANT

Le circuit précédent peut être utilisé aussi comme une source de courant où le courant drain-source  $I_D$  reste pratiquement constant, même si la tension drain-source  $V_{DS}$  varie. C'est utile pour la polarisation des transistors et pour fournir un courant de référence dans les régulateurs de tension. Le JFET en source de courant est utilisé dans les amplificateurs à plusieurs étages pour définir un courant de polarisation précis pour chaque étage, améliorant ainsi la stabilité et la performance globale du circuit.

Une fois que  $V_{DS}$  dépasse un certain seuil, le courant  $I_D$  est principalement contrôlé par la tension  $V_{GS}$  qui est déterminé par la résistance  $R_S$  ( $V_{GS}=V_G - I_D R_S$  et comme la grille est souvent reliée à la masse ( $V_G=0V$ ) donc  $V_{GS} = -I_D R_S$ ) , et devient relativement insensible aux variations de  $V_{DS}$ .

## 2.2. LES TRANSISTORS MOSFET

Parmi les inconvénients des JFETs la limitation de leur plage de tension de grille avant le pincement et leur sensibilité à la température ce qui affecte sur l'impédance d'entrée (Le courant de fuite inverse augmente avec la température) et sur le point de fonctionnement du transistor et donc réduire sa précision. Les MOSFETs ont résolu ces problèmes et d'autres par l'isolation de son grille du canal à l'aide une fine couche isolante de dioxyde de silicium ( $SiO_2$ ).

En outre, La structure planaire des MOSFETs permet une réduction plus facile de la taille du transistor ce qui permet une réduction de la consommation d'énergie par transistor et pour cela les MOSFETs sont devenus des composants dominants en électronique numérique intégrée (mémoire, micro-processeurs, circuit mixtes). On expliquera ci-dessous comment ils y sont parvenus.

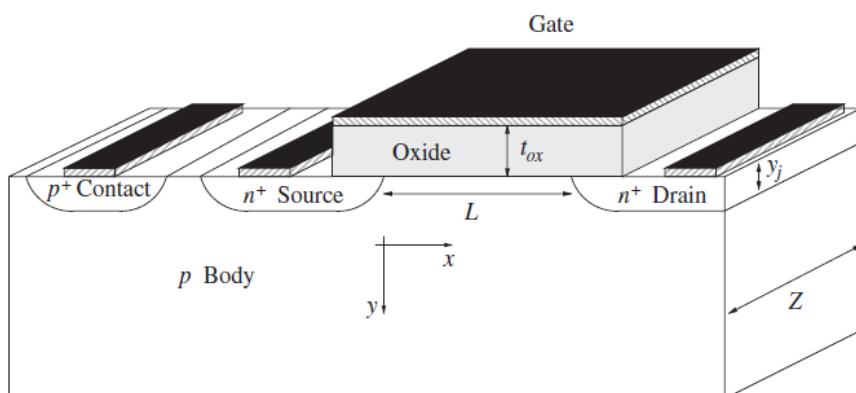

### 2.2.1. DEFINITION ET STRUCTURE

**Metal Oxide Semiconductor Field Effect Transistor** ou transistor **MOSFET** est un transistor à effet de champ composé de trois terminaux principaux : la source (S) et le drain (D) qui sont fortement dopés et la grille (G) qui est l'électrode de contrôle. Il existe également un quatrième terminal, le substrat ou 'body' (B), il dopé de manière opposé au drain et à la source il n'est utilisé ni comme port d'entrée ni comme port de sortie et il est souvent connecté à la source.

Fig 69: Structure de base d'un MOSFET

Le transistor MOSFET est un dispositif unipolaire, le courant circulant dans son canal principal entre le drain et la source est proportionnel à la tension d'entrée donc il agit aussi comme une résistance contrôlée en tension.

Il diffère d'un JFET en ce qu'il possède une électrode de grille en « oxyde métallique » qui est électriquement isolée du canal N ou P par une très fine couche de matériau isolant, généralement du dioxyde de silicium, communément appelé verre.

Cette électrode à grille métallique peut être considérée comme une plaque d'un condensateur et l'autre plaque est le canal N ou P. l'absence du passage de courant dans la grille rendra la résistance d'entrée du MOSFET extrêmement élevée de l'ordre des méga-ohms ( $M\Omega$ ) et réduira considérablement le bruit

### 2.2.2. TYPES

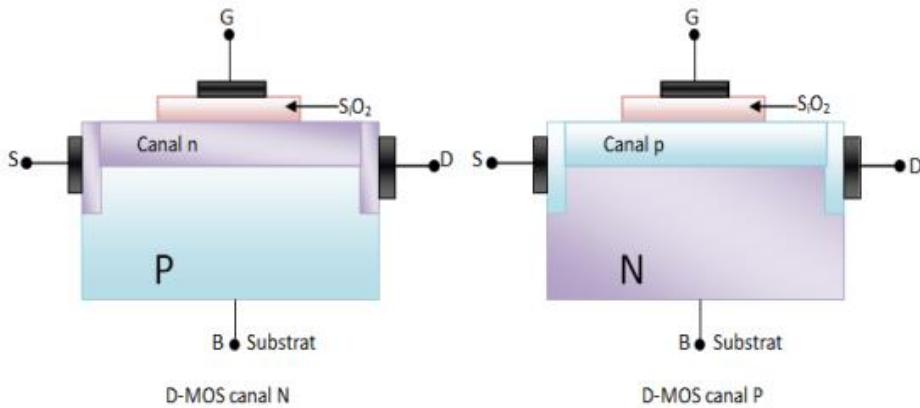

Il existe deux formes de base de MOSFET et les deux sont disponibles avec canal P (PMOS) et avec canal N (NMOS) :

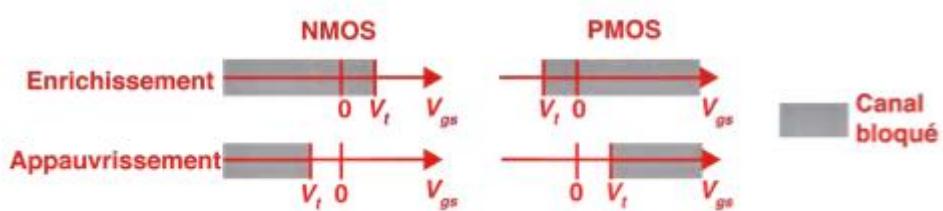

- MOSFET à appauvrissement (Depletion-MOSFET) : le transistor nécessite la tension grille-source (VGS) pour éteindre l'appareil. Le MOSFET en mode d'appauvrissement est équivalent à un interrupteur fermé parce que son canal est déjà présent entre la source et le drain même sans tension appliquée donc il est conducteur au repos ( $VGS=0$ ).

Le MOSFET à canal N fonctionne en régime d'appauvrissement avec une tension négative appliquée entre la grille et la source, et en régime d'enrichissement lorsqu'on applique une tension positive entre la grille et la source

Dans le MOSFET à appauvrissement de canal N, la tension négative de VGS épuisera le canal conducteur et le dépeuplera de ses électrons libres jusqu'à ce qu'elle éteindre le transistor. Cela signifie que plus VGS est négatif, moins il y a d'électrons dans le canal, donc le courant diminue.

L'inverse est également vrai pour le MOSFET à appauvrissement de canal P, la tension positive de VGS épuisera le canal conducteur de ses trous libres, ce qui éteindra le transistor.

Fig 70: MOSFET à appauvrissement de canal

- MOSFET à enrichissement (Enhancement-MOSFET) : il n'y a pas de canal préformé donc, le transistor est non conducteur au repos. Il devient passant à partir d'une certaine tension de grille  $V_{Th}$  (Threshold voltage) qui est la tension appliquée entre la grille et le substrat, entraînant l'inversion de la nature du substrat sous la grille.  $|V_{GS}| > |V_{Th}|$ . Le MOSFET en mode d'enrichissement est équivalent à un interrupteur ouvert.

Fig 71: MOSFET à enrichissement de canal

### 2.2.3. SYMBOLE

La ligne entre le drain (D) et la source (S) dans le symbole de transistor MOSFET représente le canal semi-conducteur. Si cette ligne est continue, elle représente un MOSFET de type d'appauvrissement

Si la ligne de canal est représentée par une ligne pointillée, elle représente un MOSFET de type. La direction de la flèche pointant vers cette ligne de canal indique que le canal conducteur est de type N

Fig 72 : Symboles d'un MOSFET à enrichissement et à appauvrissement

#### 2.2.4. PRINCIPE DE FONCTIONNEMENT

En fonction de la tension appliquée sur la grille, celui-ci sera rempli avec des charges positives ou négatives. Ce qui entraînera une modification de la répartition des charges dans le semi-conducteur, ce qui modulera la résistance du conducteur. Dans un transistor NMOS par exemple :

La tension négative sur la grille, repousse les électrons (porteurs minoritaires du substrat P) loin de l'interface et attire les porteurs majoritaires du substrat type P (trous) qui vont

s'accumuler dans une couche très fine à la surface du semiconducteur, juste sous l'oxyde de grille. C'est ce qu'on appelle **le régime d'accumulation** qui se distingue par une forte concentration de trous. Il n'y a pas un chemin conducteur entre source et drain et donc le transistor ne conduit pas entre la source et le drain et il se comporte comme un condensateur, avec l'oxyde de grille comme diélectrique.

**Le régime de déplétion** : c'est une phase transitoire dans le fonctionnement d'un transistor NMOSFET. Bien qu'il ne soit pas utilisé pour la conduction, sa compréhension est essentielle pour l'analyse des performances, la modélisation précise et l'optimisation des dispositifs MOSFET modernes.

Dans le régime de déplétion on applique une tension légèrement positive sur la grille  $V_{FB} < V_{GS} < V_{th}$  ( $V_{FB}$  tension de bandes plates. À cette tension, il n'y a pas de charge nette dans le semiconducteur près de l'interface parce que la zone de charge d'espace disparaît.) qui repousse les trous mobiles de la surface du semiconducteur et crée une zone de charge d'espace (zone de déplétion) sous l'oxyde de grille. Cette zone est désertée de porteurs de charges mobiles et contient des ions accepteurs (de Bore) fixes chargés négativement. La charge négative dans la zone de déplétion est compensée par une charge positive égale sur la grille métallique.

Le transistor ne conduit pas à cause de l'absence d'un canal conducteur entre la source et le drain.

### Le régime d'inversion

Dans ce régime le transistor devient conducteur après l'apparition d'une couche de porteurs minoritaires (électrons) à l'interface oxyde-semiconducteur due à l'application d'une tension de grille positive et suffisamment élevée (supérieur à la tension de seuil  $V_{th}$ ).

Le champ électrique intense attire les électrons vers l'interface ce qui forme une couche riche d'électrons. Cette couche agit comme un canal conducteur entre la source et le drain.

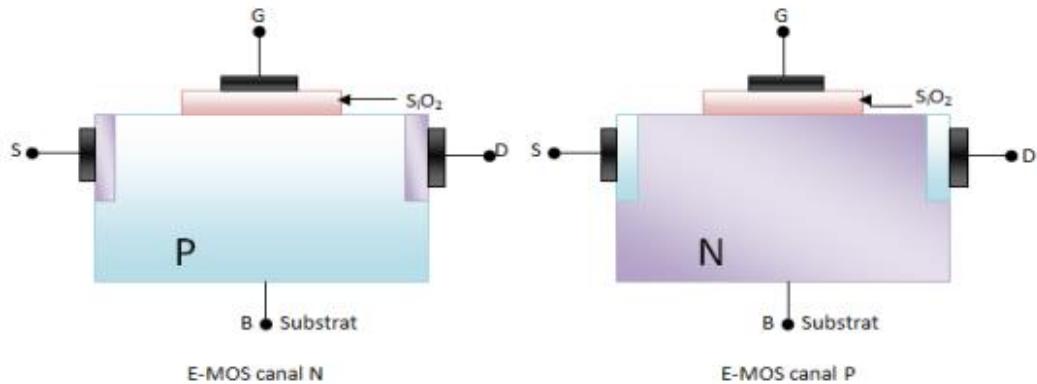

#### 2.2.5. MOSFET A APPAUVRISSEMENT DE CANAL N

**Etat par défaut ( $V_{GS}=0V$ )** : le transistor est conduit

Le courant peut circuler entre le drain et la source parce que le canal est déjà existé

**Pour  $V_{GS}>0V$**

Le canal s'élargit et le courant  $I_{DS}$  augmentera

### **Pour $V_{GS} < 0V$**

Les trous du substrat de type P vont attirer vers le canal ce qui lui rétrécit progressivement et diminue le courant

### **Pour $V_{GS} \leq V_T$**

Au-delà d'une certaine tension (tension de seuil  $V_{th}$  (threshold voltage)), le canal conducteur se ferme et le transistor devient bloqué (Off)

## **2.2.5.1. LES REGIMES DE FONCTIONEMENT D'UN MOSFET A APPAUVRISSEMENT DE CANAL N**

Le canal N existe physiquement entre la source et le drain même sans tension appliquée à la grille. La tension de seuil  $V_{th}$  est négative

### **a. Régime de Conduction**

Le MOSFET permet le passage d'un courant  $I_D$  entre le drain et la source qui est dépend de la tension  $V_{DS}$ .

### **b. Régime d'enrichissement**

Lorsque  $V_{GS} > 0V$ , les électrons du substrat de type P vont attirer vers l'interface Oxyde-SC sous la grille ce qui va élargir le canal et augmenter le courant  $I_D$  par rapport au régime de conduction normale

### **c. Régime linéaire**

Lorsque  $V_{GS} > V_{th}$  et  $V_{DS} < V_{GS} - V_{th}$ , le MOSFET se comporte comme une résistance variable contrôlée en tension. Le canal est partiellement ouvert et permet le passage d'un courant  $I_D$  qui augmente linéairement avec  $V_{DS}$  pour une valeur donnée de  $V_{GS}$ .

### **d. Régime de saturation**

Dans ce régime,  $V_{DS}$  est suffisamment élevé ( $V_{DS} > V_{GS} - V_{th}$  et  $V_{GS} > V_{th}$ ) pour que la région de canal près du drain soit pincée. Le courant  $I_D$  devient relativement constant, indépendant de  $V_{DS}$  et dépend seulement de  $V_{GS}$ .

### **e. Régime d'appauvrissement**

La tension de grille négative ( $V_{th} < V_{GS} < 0$ ) repousse les électrons partiellement les électrons du canal ce qui diminue le courant  $I_D$  par rapport au régime de conduction normale

## f. Régime de blocage

Lorsque la tension de grille devient suffisamment négative ( $V_{GS} \ll V_{th}$ ), le canal va être appauvrit de porteurs de charge empêchant ainsi le passage du courant entre le drain et la source. Le courant est très faible ou nul dans ce régime, donc le MOSFET entre dans un état de blocage

Fig 73: Régimes de fonctionnement d'un MOSFET à appauvrissement

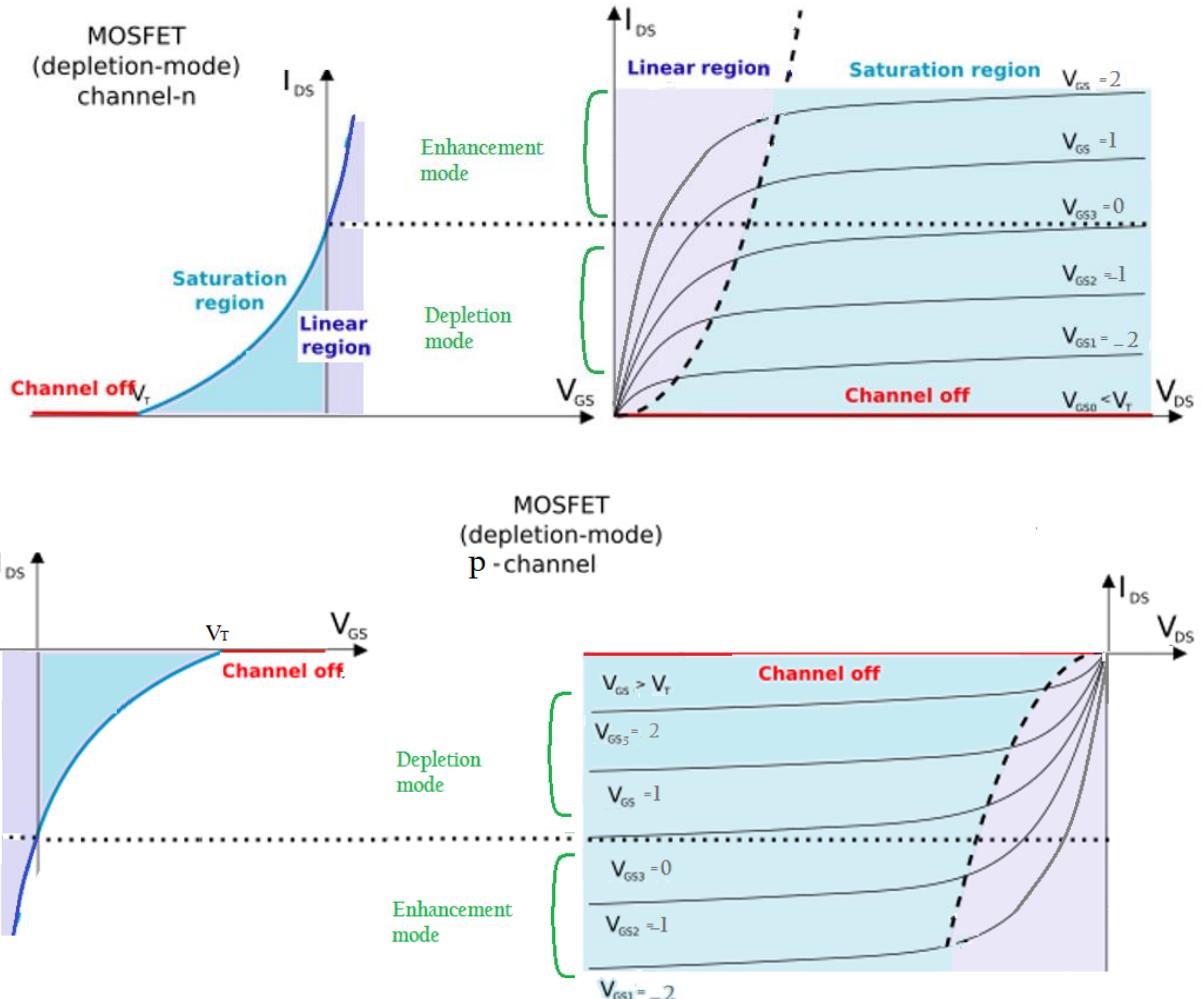

### 2.2.6. MOSFET A ENRICHISSEMENT DE CANAL N

Etat par défaut ( $V_{GS}=0V$ ) : le transistor est bloqué

Le courant ne peut pas circuler entre le drain et la source parce qu'il n'y a pas de canal

Pour  $V_{GS} < V_{th}$

La création de deux jonctions PN une est direct et l'autre est inverse va empêcher le passage de courant.

### **Pour $V_{GS} \geq V_{th}$**

Lorsqu'on atteint une certaine tension (tension de seuil  $V_{th}$  (threshold voltage)), Les électrons du substrat de type P vont attirer vers l'interface Oxyde- SC sous la grille ce qui va former un canal conducteur de type N entre le drain et la source et le transistor devient conducteur (On). Ce canal va s'élargir progressivement avec l'augmentation de la tension  $V_{GS}$  ce qui va augmenter le courant

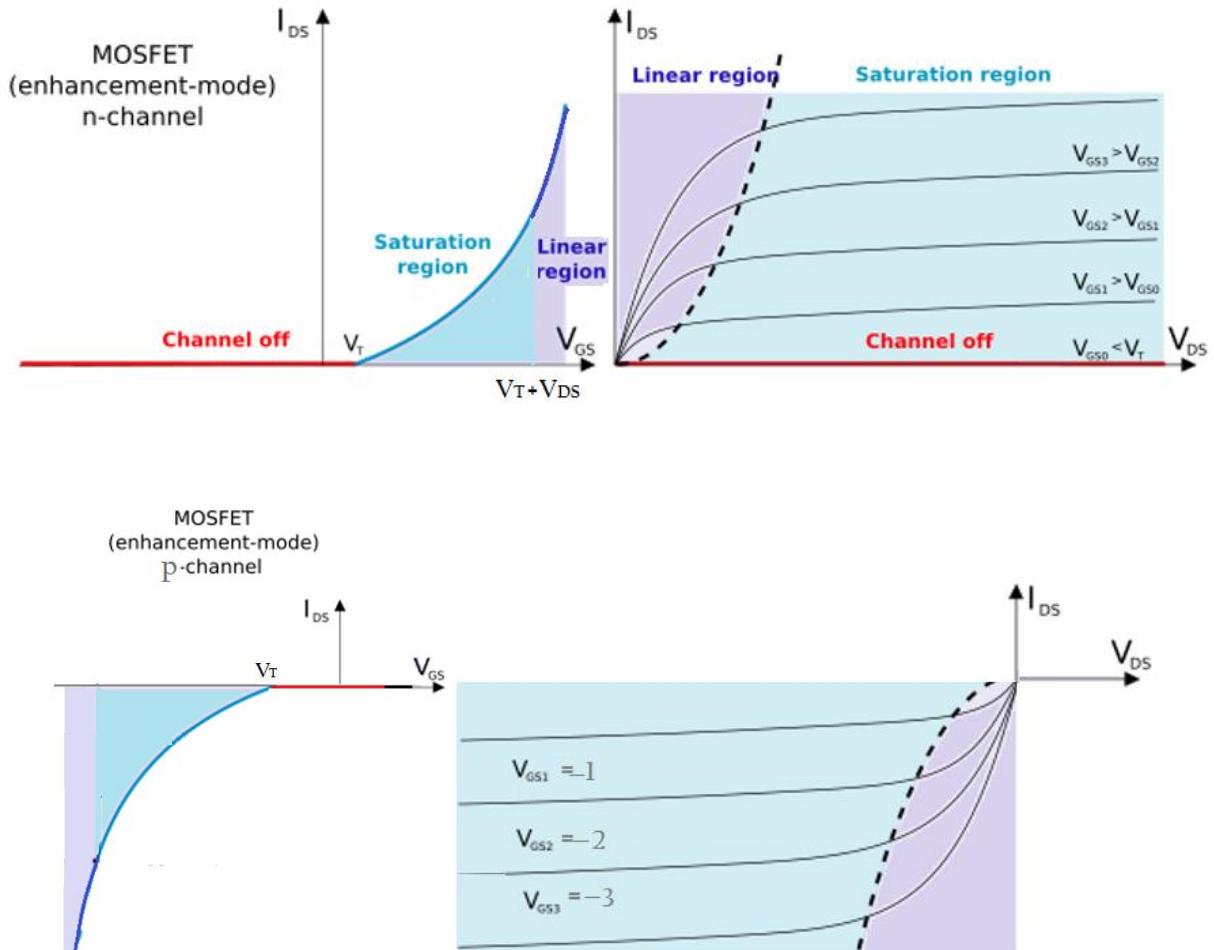

#### **2.2.6.1. LES REGIMES DE FONCTIONEMENT D'UN MOSFET A ENRICHISSEMENT DE CANAL N**

##### **a) Région de blocage (Cut-off region)**

C'est quand la tension  $V_{GS}$  est inférieure à  $V_{th}$ . Le canal dans cette région n'est pas formé mais il existe un faible courant de fuite  $I_D$  due à la présence de d'une jonction PN inverse entre le substrat de type P et le drain de type N et une jonction PN direct entre le substrat de type P et la source de type N. Le transistor est considéré comme interrupteur ouvert

##### **b) Région sous le seuil**

Lorsqu'on rapproche suffisamment à la tension de seuil  $V_{th}$ . Le courant  $I_D$  reste faible mais devient non négligeable et son comportement devient exponentiel par rapport à  $V_{GS}$ . Cette caractéristique est importante pour les applications à très basse consommation

##### **c) Région linéaire**

C'est quand la tension  $V_{GS} > V_{th}$  et  $V_{DS} < V_{GS} - V_{th}$ . Le canal dans cette région est formé et il est conducteur. L'augmentation d' $I_D$  dépend des tension  $V_{GS}$  et  $V_{DS}$ . Transistor se comporte comme une résistance contrôlée par la tension

$$I_{DS} = \beta \left[ (V_{GS} - V_t) V_{DS} - \frac{V_{DS}^2}{2} \right]$$

##### **d) Région de saturation**

C'est quand la tension  $V_{GS} > V_{th}$  et  $V_{DS} \geq V_{GS} - V_{th}$ . Le canal dans cette région est pincé près du drain. Le courant  $I_D$  relativement constant par rapport à  $V_{DS}$ , mais dépend fortement de  $V_{GS}$ . Cette région est Utilisé pour l'amplification de tension  $I_{DS} = \frac{\beta}{2} [(V_{GS} - V_t)^2]$

Fig 74: Régimes de fonctionnement d'un MOSFET à enrichissement

## 2.2.7. DOMAINE D'UTILISATION DES MOSFETs

Les propriétés spécifiques des MOSFETs tels que: l'impédance d'entrée très élevée, la possibilité d'être contrôlés par une tension très faible positive ou négative, la bonne stabilité thermique qui les rend plus fiables dans diverses conditions de fonctionnement et la possibilité d'être fabriqués à des tailles beaucoup plus petites, ce qui est crucial pour l'intégration à grande échelle. tous ces avantages ont fait les MOSFET le choix privilégié dans de nombreuses

applications, en particulier dans les circuits intégrés numériques et analogiques modernes. dans ce qui suit on va parler sur deux utilisations très fréquentes

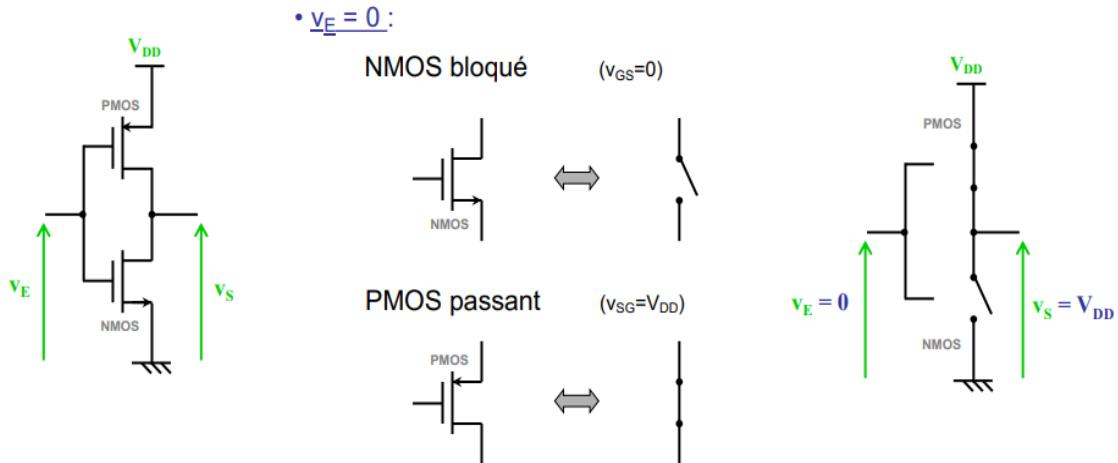

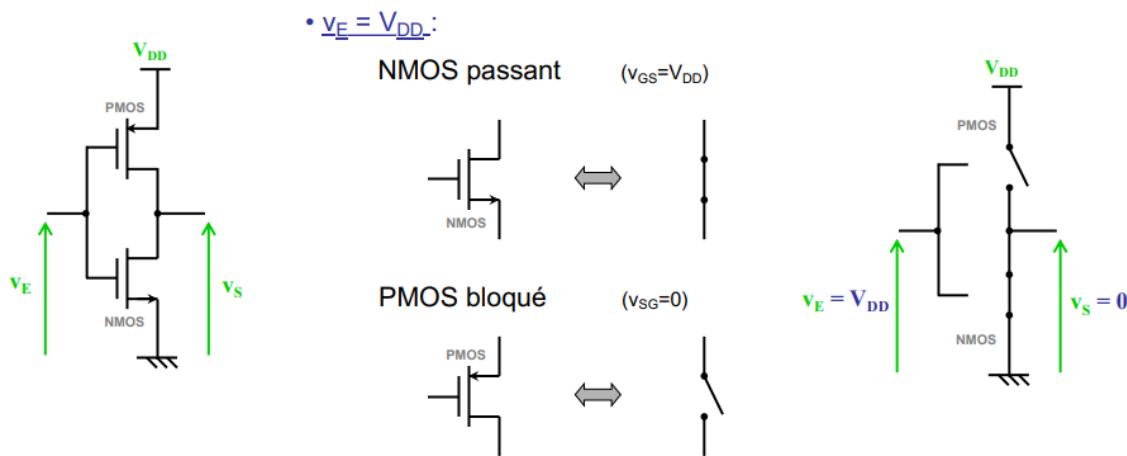

### a) L'INVERSEUR LOGIQUE CMOS (Complementary Metal-Oxide-Semiconductor)

C'est l'un des composants de base des circuits logiques numériques. Il réalise la fonction logique NOT (il inverse le signal d'entrée, le 0 devient 1 et le 1 devient 0). Il est constitué de deux transistors MOS à enrichissement complémentaires : un MOSFET de type N (NMOS) connecté à la masse GND et un MOSFET de type P (PMOS) connecté à l'alimentation  $V_{DD}$ .

❖ Quand l'entrée (la grille) est à 0V :

La source du PMOS est connectée à  $V_{DD}$  (par exemple 5V)

$$V_{GS} = V_G - V_S = 0 - 5 = -5V. \text{ Donc, PMOS est ON}$$

La source du NMOS est connectée à la masse (0 V)

$$V_{GS} = V_G - V_S = 0 - 0 = 0V. \text{ Donc, NMOS est OFF}$$

La sortie qui est formée par la connexion des deux drains est 5V

❖ Quand l'entrée (la grille) est à 1V :

La source du PMOS est connectée à  $V_{DD}$  (par exemple 5V)

$$V_{GS} = V_G - V_S = 5 - 5 = 0V. \text{ Donc, PMOS est OFF}$$

La source du NMOS est connectée à la masse (0 V)

$$V_{GS} = V_G - V_S = 5 - 0 = 5V. \text{ Donc, NMOS est ON}$$

La sortie est 0

Fig 75 : Fonctionnement d'un inverseur CMOS à  $V_E = 0V$  et à  $V_E = V_{DD}V$

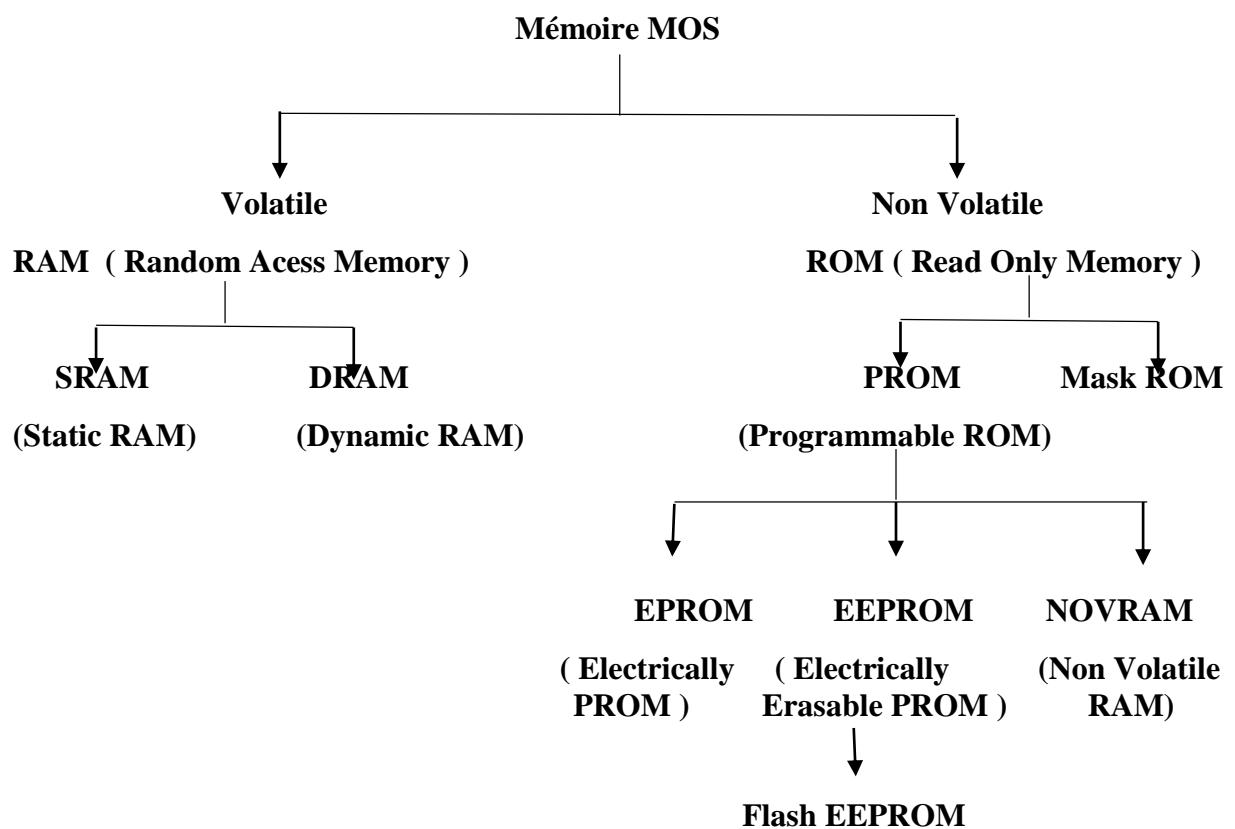

### b) LA RAM DYNAMIQUE

La RAM dynamique ou DRAM (Dynamic Random Access Memory) est un type de mémoire vive couramment utilisé dans de nombreux systèmes électroniques, notamment les ordinateurs, les smartphones, et d'autres appareils électroniques comme mémoire principale. Elle stocke les données et les programmes temporairement en cours d'exécution pour permettre un accès rapide par le processeur. La DRAM permet aux ordinateurs de fonctionner de manière efficace en offrant une grande capacité de stockage temporaire et un accès rapide aux données.

La RAM est stockée sur la carte mère dans des modules appelés DIMM, qui signifie « Dual Inline Memory Modules ». Ces modules sont des petites cartes de circuit imprimé contenant plusieurs puces de DRAM. Les types les plus répandus actuellement de DIMM sont DDR4 et DDR5 SDRAM.

La carte mère possède des slots spécifiques pour accueillir ces modules DIMM

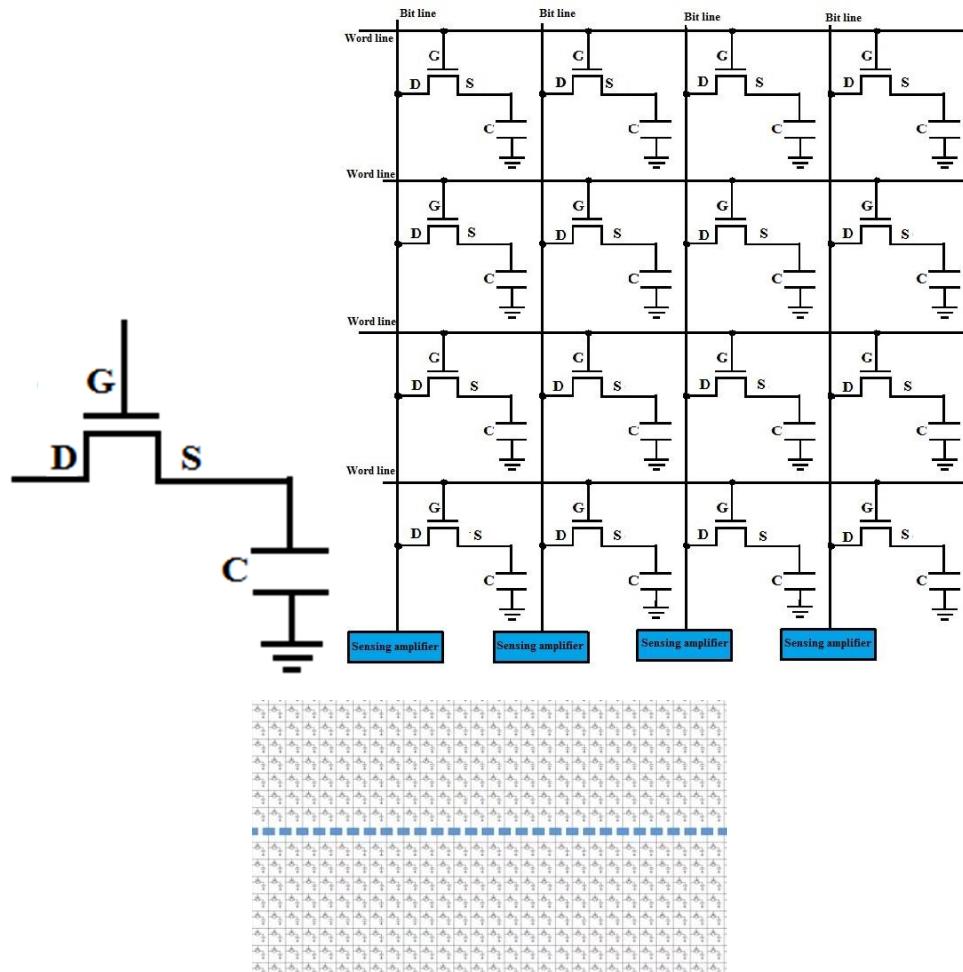

Chaque bit est stocké dans une cellule composée d'un transistor qui agit comme un interrupteur, permettant de lire ou d'écrire dans le condensateur. Le condensateur stocke les bits

d'information sous forme de charge électrique. Un '1' logique est représenté par la présence de charge, un '0' représente son absence.

La caractéristique "dynamique" de la RAM: les condensateurs ont tendance à se décharger naturellement avec le temps, même si la cellule n'est pas en train d'être lue ou écrite. Cela signifie que les données stockées dans ces cellules peuvent se perdre rapidement (en quelques millisecondes) ce qui nécessite un rafraîchissement périodique (plusieurs centaines de fois par seconde) pour maintenir les données. Ce processus est géré par le contrôleur de mémoire qui peut être intégré au processeur ou sur le chipset de la carte mère.

Le rafraîchissement consiste à lire périodiquement le contenu de chaque cellule de mémoire et à réécrire la même information dans la cellule

## STRUCTURE DE LA DRAM

La DRAM est organisée en une matrice (ou grille) de cellules de mémoire, chaque cellule contenant un condensateur et un transistor. Ces cellules sont disposées en **lignes** et **colonnes** :

**Lignes** : Appelées "Word Lines", elles sélectionnent une rangée complète de cellules.

**Colonnes** : Appelées "Bit Lines", elles transportent les données stockées dans les cellules.

Chaque cellule de mémoire est située à l'intersection d'une ligne et d'une colonne.

Pour lire ou écrire des données dans une cellule de mémoire, voici ce qui se passe :

1. Quand le CPU a besoin de lire ou d'écrire des données en mémoire, il envoie une requête sur le bus système. Cette requête contient l'adresse mémoire concernée (l'adresse de ligne et l'adresse de colonne) et le type d'opération (lecture ou écriture).

2. Avant de lire la donnée dans une cellule DRAM, les lignes de bit sont d'abord préchargées à une tension de référence, généralement la moitié de la tension d'alimentation  $V_{DD}$ . Cela garantit que les lignes de bit prêtent à être influencées par la charge du condensateur.

3. Sélection de la Ligne : Le contrôleur de mémoire active la ligne de mot 'Word Line' correspondante à la rangée où se trouve la cellule.

NB :

- ❖ Le contrôleur de mémoire est un circuit intégré ou une partie d'un circuit intégré qui gère le flux de données entre le processeur (CPU) et la mémoire vive (RAM). Dans les architectures modernes, il est souvent intégré directement dans le processeur ou dans le chipset de la carte mère.

- ❖ Activer une Word Line signifie appliquer une tension à cette ligne ce qui va activer Le signal RAS "Row Address Strobe" (impulsion d'adresse de ligne) qui est un signal de contrôle utilisé dans les mémoires DRAM pour indiquer que l'adresse de ligne est valide et prête à être lue. L'application de cette tension mette en conduction tous les transistors de cette ligne. Donc les transistors se comportent comme des interrupteurs fermés et le courant va déplacer vers le condensateur. La charge stockée dans les condensateurs des cellules commence à se déplacer vers les lignes de bit. Après un court délai la tension sur la ligne de bit se **stabilise**.

- Si le condensateur de la cellule est **chargé** (indiquant un 1), il partage une petite partie de sa charge avec la ligne de bit, ce qui fait monter légèrement la tension sur la ligne de bit.

- Si le condensateur est **déchargé** (indiquant un 0), la ligne de bit reste proche de sa tension de précharge.

4. L'amplificateur de détection est préalablement en état d'équilibre, il détecte la légère variation de tension. La faible différence de tension entre les deux entrées de l'amplificateur entraîne un léger déséquilibre. L'amplificateur de détection amplifie ce déséquilibre ou cette différence de tension et "décide" si la cellule contient un 1 ou un 0.

5. Sélection de la Colonne : L'adresse de colonne est ensuite placée sur le bus d'adresse et le signal CAS (Column Address Strobe) est activé, sélectionnant une cellule spécifique dans la ligne activée. Les données de cette cellule sont alors lues à partir de l'amplificateur de détection correspondant.

6. **Une fois que la stabilisation de la ligne de bit est complète et que l'amplificateur de détection a interprété les données** sur la ligne de bit choisie, les données de la cellule sélectionnée peuvent être lues.

- En théorie, dans les DRAM classiques, **CAS** est activé **après** la stabilisation complète de la ligne de bit.

- En pratique, dans les DRAM modernes (comme DDR), pour améliorer les performances, **CAS** est envoyé **un peu avant** la stabilisation complète de la ligne de bit

Si c'est une opération de **lecture**, les données sont récupérées par le contrôleur et envoyées au CPU ou à l'appareil qui a demandé la donnée à travers le bus système.

7. Après avoir lu les données, la charge dans le condensateur de la cellule est partiellement dissipée. Pour préserver les données, un processus de **réécriture** ou **rafraîchissement** est effectué. L'amplificateur de détection restaure la charge d'origine dans le condensateur

- ❖ Si la cellule contenait un 1 (condensateur chargé), la charge est **réinjectée** dans le condensateur pour le recharger.

- ❖ Si la cellule contenait un 0 (condensateur déchargé), l'absence de charge est **maintenue**, et le condensateur reste déchargé.

8. Après la restauration de la charge, le transistor MOSFET est refermé en **désactivant** la ligne de mot (Word Line), isolant à nouveau le condensateur de la ligne de bit et la ligne de bit est ensuite **préchargée** de nouveau à sa tension de référence ( $VDD/2$ ) pour préparer les cellules à la prochaine opération (lecture ou écriture).

### 3. TRANSISTOR MOS A GRILLE FLOTTANTE

Fig : Classification des principales mémoires MOS.

Contrairement aux transistors MOS traditionnels utilisés dans la DRAM, un transistor à grille flottante permet de stocker une charge sur une longue période, même après que l'alimentation électrique est coupée.

Les mémoires à grille flottante sont largement utilisés dans divers domaines liés au stockage de données et aux dispositifs électroniques nécessitant une mémoire non volatile.

Cette technologie est très utilisée dans les clés USB, les cartes mémoires SD, les disques SSD, les mémoires des tablettes et smartphones ...etc.

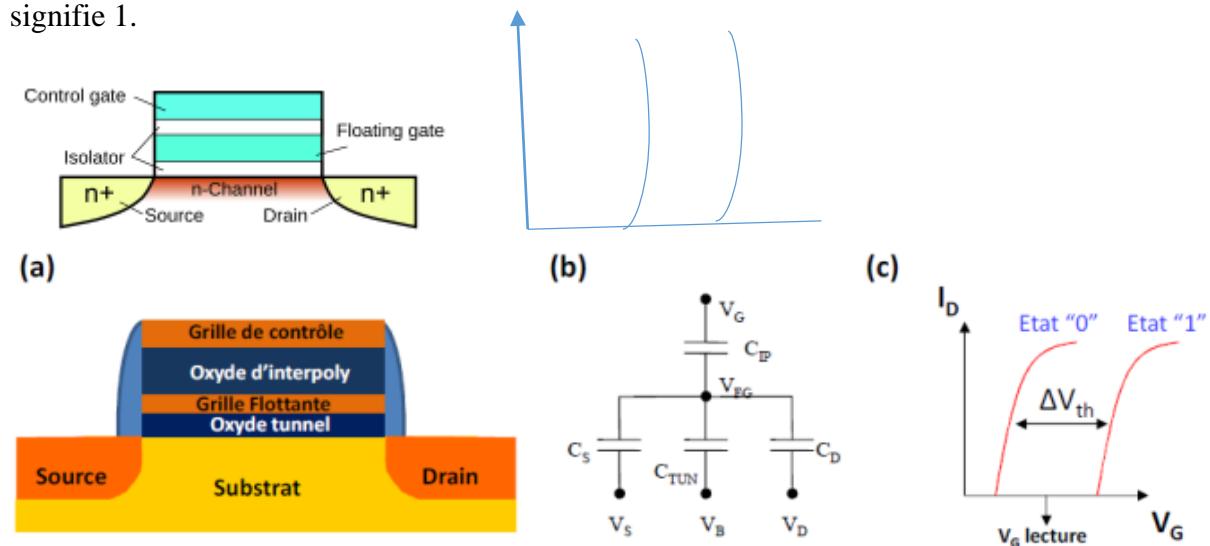

Elle composé d'un transistor MOS avec une grille flottante qui est une couche conductrice (généralement en polysilicium) isolée de la grille de contrôle par l'oxyde de contrôle et isolée du canal par l'oxyde tunnel. La grille de contrôle est responsable de produire le champ électrique qui attire ou repousse les électrons. La grille flottante agit comme un conteneur. Elle piège l'électron et la mémoire flash fonctionne en ajoutant ou en supprimant un électron de la grille flottante. Lorsque l'électron est présent dans la grille, cela signifie 0 et lorsqu'il est absent, cela signifie 1.

A cross-section of a floating-gate transistor

NB :

- ❖ L'isolation de la grille flottante permet de conserver les charges pendant de longues périodes (typiquement  $>10$  ans).

- ❖ La qualité de l'oxyde est cruciale pour éviter les fuites de charges.

- ❖ Les électrons sont injectés dans la grille flottante par injection de porteurs chauds ou par effet tunnel Fowler-Nordheim

#### Mécanismes d'injection de charge dans la grille flottante

Il existe deux principaux mécanismes d'injection de charge dans les mémoires à grille flottante :

1. Injection de porteurs chauds (Hot Carrier Injection - HCI)

2. Effet tunnel Fowler-Nordheim (FN)

1. Injection de porteurs chauds (HCI) :

Après l'application une forte tension sur le drain (entre 4 et 5V, la source et le substrat seront liés à la masse) et sur la grille de contrôle (8-10V), certains électrons dans le canal deviennent très énergétiques ("chauds"). Ces électrons chauds peuvent sauter et entrer dans la barrière d'oxyde et juste une fraction de ces électrons atteint la grille flottante (de 0.001% à 0.01%), où ils restent piégés (ils ne peuvent pas s'échapper en raison de la barrière de potentiel de l'oxyde)

## 2. Effet tunnel Fowler-Nordheim (FN) :

Se produit après l'application d'une très forte tension sur la grille (15- 20V) ce qui réduit la barrière énergétique de l'isolant pour permettre aux électrons de se traverser la barrière. Ce mécanisme exploite les principes de la mécanique quantique pour déplacer les électrons même si leur énergie est inférieure à celle de la barrière

### Comparaison et utilisation de ces mécanismes

- HCI est souvent utilisé pour la programmation (écriture des données) dans les mémoires NOR Flash et dans les EPROM

- FN est utilisé pour l'effacement dans les NOR Flash et pour la programmation et l'effacement dans les NAND Flash

- Le choix dépend des compromis entre vitesse, consommation et durée de vie du dispositif

**# Processus de lecture :** La lecture est équivalente à la détection de l'état de conduction du transistor. Elle se fait par :

- La mise à la masse de la source.

- L'application d'une tension d'environ 1V sur le drain.

- L'application d'une tension de 4 à 5V sur la grille de contrôle.

- La mesure de la tension de seuil du transistor et du courant circulant entre la source et le drain (un transistor chargé aura une tension de seuil plus élevée qu'un transistor non chargé.)

- Si la grille flottante est vide (état logique '1') :

\* La tension de seuil est basse.

\* Le courant significatif est mesuré. Donc le transistor conduit

- Si la grille flottante contient des électrons (état '0') :

\* La tension de seuil est élevée

\* Un courant mesuré est faible ou nul. Donc le transistor ne conduit pas

**# Processus d'écriture (programmation) :** L'écriture est l'injection d'électrons dans la grille flottante pour modifier les propriétés électriques du transistor et ainsi stocker des données. Ce processus diffère légèrement selon le type de mémoire (EPROM, EEPROM, ou Flash)

- Premièrement, la cellule doit être dans l'état effacé (représentant un '1').

- On utilise le mécanisme d'injection par porteurs chauds (HCl) dans les **EPROM** pour charger la grille flottante

- On utilise le mécanisme d'effet tunnel Fowler Nodheim (FN) dans les **EEPROM** et **FLASH** pour charger la grille flottante

- Le fort champ électrique appliqué permet d'injecter des électrons dans la grille flottante ce qui modifie la tension de seuil du transistor

- Les charges négatives stockées dans la grille flottante agissent comme une tension négative qui s'oppose au champ créé par la grille de contrôle.

- Pour compenser cet effet et activer le transistor, une tension de grille plus élevée ( $V_{th2} > V_{th1}$ ) est nécessaire.

### **# Processus d'effacement :**

L'effacement c'est le retrait des électrons de la grille flottante pour ramener le dispositif à son état initial. Le mécanisme d'effacement varie selon le type de mémoire.

Dans les EPROM, l'effacement se fait par l'exposition des électrons piégés dans la grille flottante aux UV ce qui leur permet de quitter la grille flottante et de retourner au substrat ou à d'autres parties du transistor.

Dans les EEPROM et Flash, l'effacement se fait par l'effet tunnel Fowler-Nordheim. Un champ électrique intense est appliqué pour permettre aux électrons de traverser l'oxyde tunnel par effet tunnel.

NB : Toutes les cellules du bloc sont d'abord lues pour identifier celles qui nécessitent un effacement.

- Les cycles répétés d'écriture/effacement dégradent progressivement l'oxyde tunnel et limite le nombre de cycles possibles (typiquement  $10^4$  à  $10^6$  cycles).

**Comparaison des processus d'effacement :**

| Type de mémoire | Méthode d'effacement         | Sélectivité                    |

|-----------------|------------------------------|--------------------------------|

| <b>EPROM</b>    | Exposition aux UV            | Effacement total               |

| <b>EEPROM</b>   | Effet tunnel Fowler-Nordheim | Effacement cellule par cellule |

| <b>Flash</b>    | Effet tunnel Fowler-Nordheim | Effacement par blocs           |